# AMD XILINX

# A Technique to Reduce Cross Talk Between Copper Routes Under a 1 mm Pitch BGA

### Abstract

This white paper describes a technique for reducing cross talk between copper routes in 1 mm pitch BGA devices. This method can be used with any integrated circuit device that uses a 1 mm BGA package. The technique is a printed circuit board (PCB) level solution, and is employed at the layout level of a design. This white paper is targeted for:

- Printed circuit board design engineers

- Simulation engineers

- Layout engineers

Xilinx is creating an environment where employees, customers, and partners feel welcome and included. To that end, we're removing noninclusive language from our products and related collateral. We've launched an internal initiative to remove language that could exclude people or reinforce historical biases, including terms embedded in our software and IPs. You may still find examples of non-inclusive language in our older products as we work to make these changes and align with evolving industry standards. Follow this link for more information.

1

XII INX

### Introduction

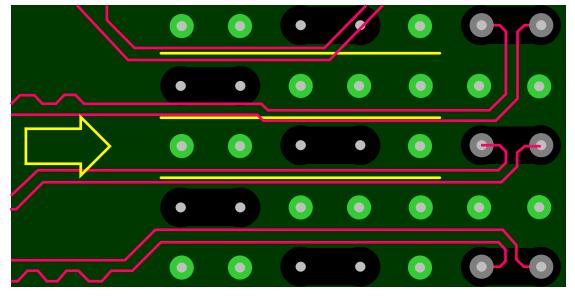

This white paper describes a technique to reduce cross talk between signal routes under a 1 mm pitch BGA, without losing significant PCB real estate for outer breakout routing. The traditional BGA breakout is one BGA pin and one via to allow routing on internal layers. A typical high-speed interface at the BGA breakout using impedance controlled differential pair routing is the standard way of implementing BGA breakout of 1 mm pitch devices. By using the rule of 1 pin 1 via breakout, as shown in the following figure, and the correct selection of stack-up to allow the correct line width and pitch, it is possible to route multiple high-speed differential pairs from the BGA to any target device or connector. This technique to reduce cross talk uses multiple vias in parallel at the point of breakout. The multiple vias are arranged in such a way as to not disturb the normal routing of signals in the BGA breakout region. This is done by using smaller vias that can be fitted closer together.

### Figure 1: Traditional 1 mm Pitch BGA Breakout Using a One Pin, One Via Solution

X27080-091422

# **Background on Traditional Techniques**

A typical BGA pin is 0.5 mm/19.68th pad, with a 45-degree breakout. The traditional clearance rules to manufacture a PCB include:

- 9 mil drill to trace

- 3 mil trace to trace on internal

- 4 mil trace to trace on outer layers

- 8 mil via drill (finished hole size)

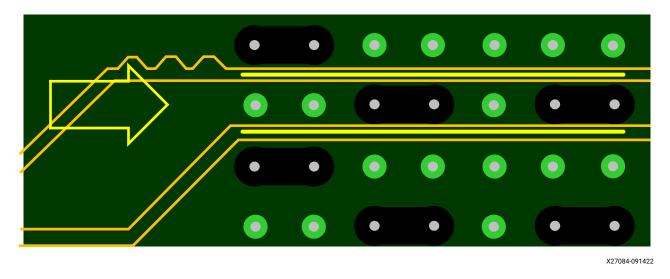

Inside the BGA breakout, exit lanes are created to allow the internal routing of signals from under the BGA region. The typical *1 pin 1 via* 45° breakout creates a structure as shown in the following figure.

Figure 2: Internal Routing Lanes

X27081-091422

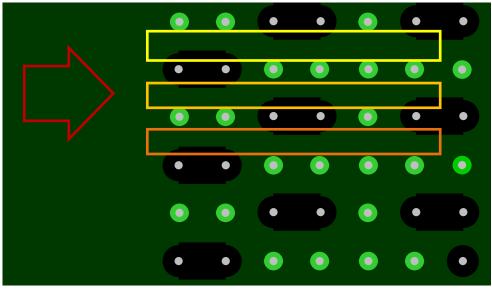

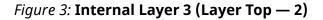

This 1 pin 1 via structure is used to create routing lanes on multiple internal layers to allow a clear area for breakout. The following figures show routing on internal layers below the BGA device to break out multiple differential signal pairs.

Figure 4: Internal Layer 5 (Layer Top — 4)

X27083-091422

Figure 5: Internal Multiple Layers of Available Routing

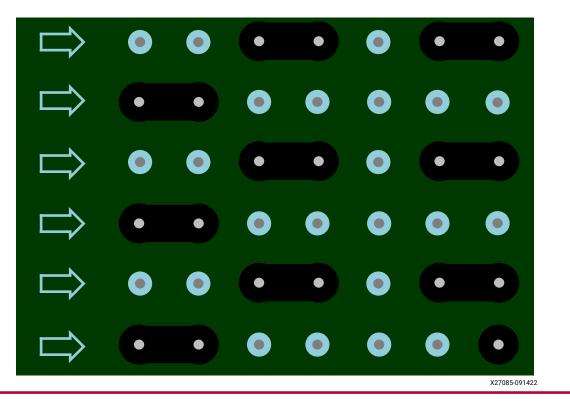

**IMPORTANT!** These lanes must be maintained to allow the practical use of 1 mm pitch BGA. The vias are arranged in a 1 mm pitch manner equally spaced (see the following figure).

#### Figure 6: Lanes Maintained to Allow Practical Use of 1 mm Pitch

### **Multi Via Solution**

Due to improved production processes, it is now possible to use smaller via constructions on PCBs with little increase in cost or decrease in yield.

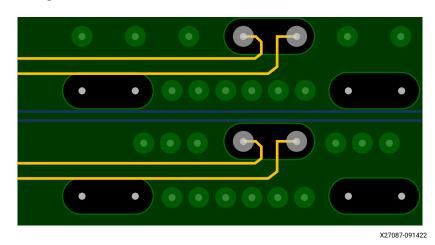

Tighter rules for the stable manufacturing of PCBs can now be used to provide new solutions. Instead of using the 1 pin 1 via solution, multiple smaller vias can be used in the same space. It is important to only add extra vias in a horizontal line to maintain the exit lanes for routing. Also, when possible, the pin pad size should be reduced to 80% of normal. In the example shown in the following figure, the pin pad size is reduced down to 0.4 mm/15.75th (which is also allowable for small pitch BGA devices). This creates enough room to add additional vias. If the new vias are connected to ground, the signal-to-signal cross talk is reduced. The following figure shows reduced BGA pins and via size, as well as the addition of multiple vias around a noise source signal such as a high-speed differential pair.

Figure 7: Reduced BGA Pin and Via Size

X27086-091422

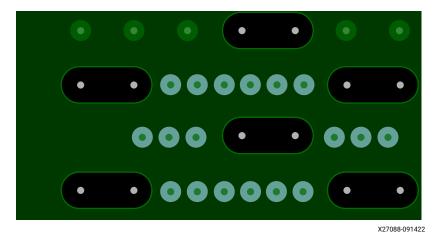

The following figure shows internal lanes that are still available for BGA breakout without breaking the design for the manufacturing rules.

#### Figure 8: Internal Lanes Available for BGA Breakout

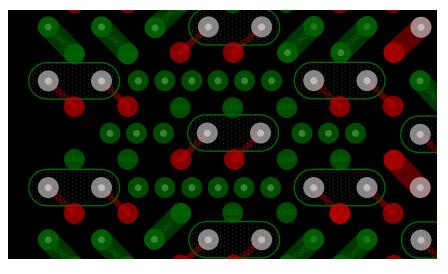

In the following figure, new ground vias are highlighted.

#### Figure 9: New Ground Vias

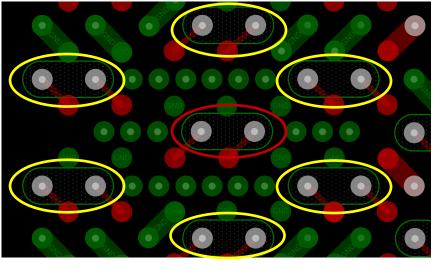

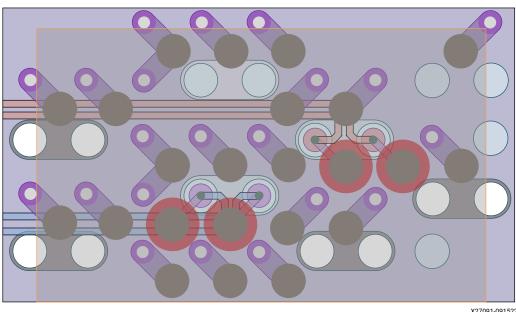

In the following figure, the pair in the red circle is the noise source and the pairs in the yellow circles are the noise recipients. There is a reduction in simulated cross talk with this method.

### Figure 10: Noise Source and Recipient

X27089-091422

# **Simulation of Cross Talk**

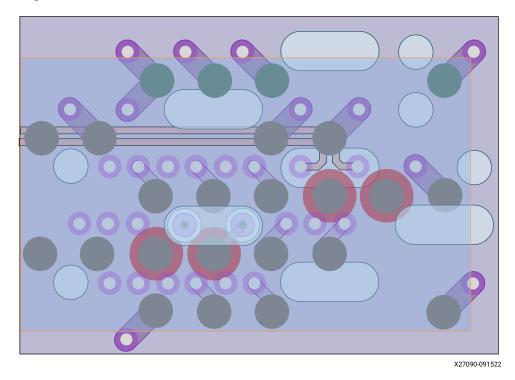

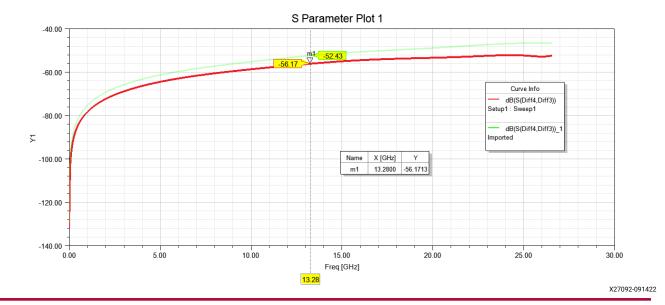

The simulation results show an improvement of 3.74 dB at 13.28 GHz when using the multi via solution over the standard 1 via per pad solution, as shown in the following figures. The intended use case for this example is a network card running at a data rate of 25 Gb/s. Therefore, the measurement was taken above 12.5 GHz to ensure the result is above the Nyquist frequency.

*Figure 11:* **Red: With GND Vias: -56.17 dB NEXT Between TX and RX**

Figure 12: Green: Without GND Vias: -52.43 dB NEXT Between TX and RX

X27091-091522

In the following figure, the green line indicates the original cross talk value when using 1 GND via per pad. Without GND vias, it is -52.43 dB NEXT between TX and RX. The red line indicates a new cross talk value when using a multiple GND via solution. With GND vias, it is -56.17 dB NEXT between TX and RX.

### Figure 13: S Parameter Plot 1

# Conclusion

This white paper outlines a technique to reduce cross talk between copper routes by reducing the impedance to ground using more local ground vias. In the example described, the simulated gain was 3.74 dB at Nyquist. The via count between routes can be maximized by the careful selection of the pad or drill size. This use case might not be suitable for all designs. Care must be taken at the design stage to ensure that the final board can be manufactured.

**RECOMMENDED:** Consult your PCB manufacturing facility on current production techniques before using this solution.

# **Revision History**

The following table shows the revision history for this document.

| Section                | Revision Summary |

|------------------------|------------------|

| 09/23/2022 Version 1.0 |                  |

| Initial release.       | N/A              |

# **Please Read: Important Legal Notices**

The information disclosed to you hereunder (the "Materials") is provided solely for the selection and use of Xilinx products. To the maximum extent permitted by applicable law: (1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with, the Materials (including your use of the

Materials), including for any direct, indirect, special, incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same. Xilinx assumes no obligation to correct any errors contained in the Materials or to notify you of updates to the Materials or to product specifications. You may not reproduce, modify, distribute, or publicly display the Materials without prior written consent. Certain products are subject to the terms and conditions of Xilinx's limited warranty, please refer to Xilinx's Terms of Sale which can be viewed at https:// www.xilinx.com/legal.htm#tos; IP cores may be subject to warranty and support terms contained in a license issued to you by Xilinx. Xilinx products are not designed or intended to be fail-safe or for use in any application requiring fail-safe performance; you assume sole risk and liability for use of Xilinx products in such critical applications, please refer to Xilinx's Terms of Sale which can be viewed at https:// www.xilinx.com/legal.htm#tos.

### **AUTOMOTIVE APPLICATIONS DISCLAIMER**

AUTOMOTIVE PRODUCTS (IDENTIFIED AS "XA" IN THE PART NUMBER) ARE NOT WARRANTED FOR USE IN THE DEPLOYMENT OF AIRBAGS OR FOR USE IN APPLICATIONS THAT AFFECT CONTROL OF A VEHICLE ("SAFETY APPLICATION") UNLESS THERE IS A SAFETY CONCEPT OR REDUNDANCY FEATURE CONSISTENT WITH THE ISO 26262 AUTOMOTIVE SAFETY STANDARD ("SAFETY DESIGN"). CUSTOMER SHALL, PRIOR TO USING OR DISTRIBUTING ANY SYSTEMS THAT INCORPORATE PRODUCTS, THOROUGHLY TEST SUCH SYSTEMS FOR SAFETY PURPOSES. USE OF PRODUCTS IN A SAFETY APPLICATION WITHOUT A SAFETY DESIGN IS FULLY AT THE RISK OF CUSTOMER, SUBJECT ONLY TO APPLICABLE LAWS AND REGULATIONS GOVERNING LIMITATIONS ON PRODUCT LIABILITY.

### Copyright

© Copyright 2022 Advanced Micro Devices, Inc. Xilinx, the Xilinx logo, Alveo, Artix, Kintex, Kria, Spartan, Versal, Vitis, Virtex, Vivado, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners.