# 模拟信号调理(OPAMP)入门

## 简介

作者: Radu Toma 和 Martin Mostad, Microchip Technology Inc.

模拟信号调理(OPAMP)外设具有最多三个内部运算放大器(运放)。它有助于降低或消除电子设计中对外部/分立运 放的需求,从而有可能精简物料清单。运放的主要用途是提前对单片机将要采集(和进一步数字处理)的模拟信号进 行调理,或者在控制应用中提供所需的输出驱动。

本技术简介将介绍 AVR® DB MCU 器件的模拟信号调理模块(OPAMP)部分如何工作。首先介绍最简单的配置,其 他更为复杂的配置均以此为基础。主要介绍的拓扑如下:

- 运放直接连接到引脚:

- 最简单、最基本的配置, 灵活度最高, 包含外部连接及元件。

- 电压跟随器或单位增益缓冲器:

- 将高阻抗输入转换为低阻抗输出的通用配置。

- 同相可编程增益放大器:

- 通过内部反馈电阻网络实现可编程增益信号放大。

- 使用两个运放的差分放大器:

- 通过共模电压抑制实现差分输入电压放大。

- 使用三个运放的仪表放大器:

- 将高输入阻抗转换为低输出阻抗的差分信号放大。

注: 代码示例针对 AVR128DB48 Curiosity Nano 评估工具包(EV35L43A)而设计,可从 GitHub 获取。Atmel Studio、MPLAB® X IDE 以及 Atmel START 和 MCC 示例均有各自独立的代码示例。本技术简介中仅详细介绍用于独 立示例的代码,但所有示例的功能均相同。有关 Atmel START 和 MCC 中的 OPAMP 模块的介绍,请分别参见 3. Atmel START 和 4. MPLAB® X MCC。

# 硬件配置

代码示例针对 AVR128DB48 Curiosity Nano 评估工具包(EV35L43A)而开发。

## 图 1. AVR128DB48 Curiosity Nano

# 目录

| 简介  | ·                                                    | 1  |  |  |  |  |

|-----|------------------------------------------------------|----|--|--|--|--|

| 硬件  | 牛配置                                                  | 2  |  |  |  |  |

| 1.  | 概述                                                   | 5  |  |  |  |  |

| 2.  | 相关器件                                                 |    |  |  |  |  |

|     | Atmel START                                          |    |  |  |  |  |

| 3.  |                                                      |    |  |  |  |  |

| 4.  | MPLAB® X MCC                                         |    |  |  |  |  |

| 5.  | MPLAB <sup>®</sup> Mindi <sup>™</sup> 模拟仿真器          | 11 |  |  |  |  |

| 6.  | MPLAB 数据可视化器                                         | 12 |  |  |  |  |

| 7.  | 运放基本配置                                               | 14 |  |  |  |  |

|     | 7.1. 用例                                              | 14 |  |  |  |  |

|     | 7.2. MPLAB Mindi 模型                                  |    |  |  |  |  |

|     | 7.3. 寄存器配置                                           | 15 |  |  |  |  |

| 8.  | 电压跟随器                                                | 21 |  |  |  |  |

|     | 8.1. 用例                                              | 21 |  |  |  |  |

|     | 8.2. 使用 MPLAB Mindi 进行电压跟随器模拟仿真                      |    |  |  |  |  |

|     | 8.3. 寄存器配置                                           |    |  |  |  |  |

|     |                                                      |    |  |  |  |  |

| 9.  | 同相可编程增益放大器                                           |    |  |  |  |  |

|     | 9.1. 用例                                              |    |  |  |  |  |

|     | 9.2. 使用 MPLAB Mindi 进行同相 PGA 模拟仿真         9.3. 寄存器配置 |    |  |  |  |  |

|     | 9.4. 以数据形式传输到 MPLAB <i>数据可视化器</i>                    |    |  |  |  |  |

| 10  | 差分放大器                                                |    |  |  |  |  |

| 10. | 10.1. 用例                                             |    |  |  |  |  |

|     | 10.2. 使用 MPLAB Mindi 进行差分放大器模拟仿真                     |    |  |  |  |  |

|     | 10.3. 寄存器配置                                          |    |  |  |  |  |

|     | 10.4. 以数据形式传输到 MPLAB <i>数据可视化器</i>                   | 37 |  |  |  |  |

| 11. | 仪表放大器                                                | 38 |  |  |  |  |

|     | 11.1. 用例                                             |    |  |  |  |  |

|     | 11.2. 使用 MPLAB Mindi 进行仪表放大器模拟仿真                     |    |  |  |  |  |

|     | 11.3. 寄存器配置                                          |    |  |  |  |  |

|     | 11.4. 以数据形式传输到 MPLAB <i>数据可视化器</i>                   | 44 |  |  |  |  |

| 12. | 参考资料                                                 | 45 |  |  |  |  |

| 13. | 版本历史                                                 | 46 |  |  |  |  |

| Microchip 网站       | 47 |

|--------------------|----|

| 产品变更通知服务           | 47 |

| 客户支持               | 47 |

| Microchip 器件代码保护功能 | 47 |

| 法律声明               | 47 |

| 商标                 | 48 |

| 质量管理体系             | 48 |

| 全球销售及服务网点          | 49 |

## 1. 概述

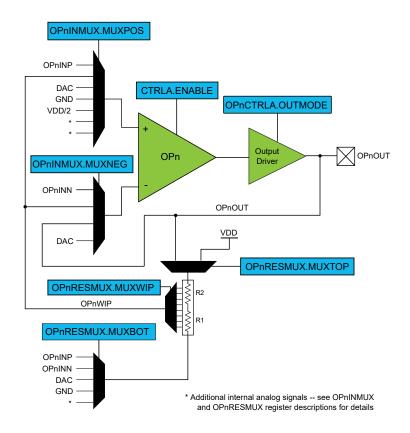

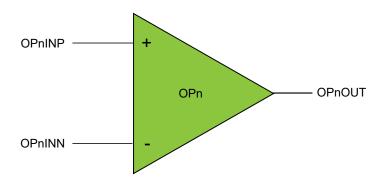

模拟信号调理(OPAMP)外设具有一个、两个或三个运算放大器(运放),统称为 OPn(其中 n 为 0、1 或 2)。这些运放支持灵活连接模拟多路开关与梯形电阻网络,可实现大量模拟信号调理配置,其中许多配置都不需要外部元件。通过每个运放同相(+)输入端的多路开关,可以连接外部引脚、梯形电阻网络的抽头位置、DAC 输出、地或  $V_{DD}/2$ 。通过每个运放反相(-)输入端的另一个多路开关,可以连接外部引脚、梯形电阻网络的抽头位置、运放的输出或 DAC 输出。每个梯形电阻网络连接到的另外三个多路开关提供了额外的配置灵活性。其中两个多路开关选择梯形电阻网络的顶部和底部连接,第三个多路开关控制抽头位置。

#### 图 1-1. 框图

表 1-1. 信号说明

| 信号名称   | 类型   | 说明             |

|--------|------|----------------|

| OPnINP | 模拟输入 | OPn 的同相(+)输入引脚 |

| OPnINN | 模拟输入 | OPn 的反相(-)输入引脚 |

| OPnOUT | 模拟输出 | OPn 的输出        |

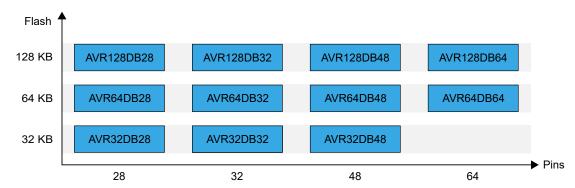

## 2. 相关器件

本节列出了本文档的相关器件。下图给出了不同系列的器件之间的关系,并注明了不同的引脚数与存储器大小:

- 从下到上迁移无需修改代码,因为这些器件的引脚彼此兼容,后者可提供相同甚至更多的功能

- 从右到左迁移会减少引脚数,进而减少可用的功能

- 具有不同闪存大小的器件通常也具有不同的 SRAM 和 EEPROM

## 图 2-1. AVR® DB 系列概览

## 3. Atmel START

Atmel START 带有 OPAMP 模块的驱动程序,可轻松配置该模块。Atmel START 模块具有 9 种预定义配置以及自定义模式。

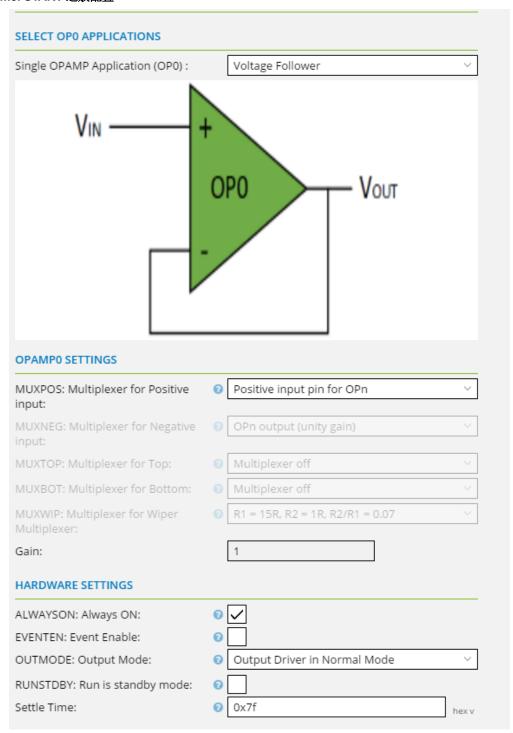

图 3-1. Atmel START 初始配置

在模块的顶部(如图 3-1 所示),可以为模块设置几个全局选项,例如使能模块,在调试模式下使能模块,以及选择输入范围。在"Component Signals"(元件信号)下,可以选择输入和输出引脚。选择引脚后将关闭选定引脚的数字输入缓冲器。因此,建议选择所有使用的引脚。"Select OPAMP Combination"(选择 OPAMP 组合)选项用于选择哪些运放采用独立配置,哪些运放组合起来构建多运放配置。所有运放都可以采用任何单运放配置,但某些多运放配置仅适用于特定的运放。有关可能组合的概述,请参见表 3-1。

表 3-1. 多运放配置

| 运放组合        | 可能的配置                               |

|-------------|-------------------------------------|

| OP1-OP2     | 差分放大器,级联(两个)同相 PGA,级联(两个)反相 PGA     |

| OP2-OP1     | 差分放大器,级联(两个)同相 PGA,级联(两个)反相 PGA     |

| OP2-OP0     | 差分放大器,级联(两个)反相 PGA                  |

| OP0-OP1-OP2 | 仪表放大器,级联(三个)同相 PGA,级联(三个)反<br>相 PGA |

| OP1-OP2-OP0 | 仪表放大器,级联(三个)反相 PGA                  |

| OP2-OP0-OP1 | 仪表放大器,级联(三个)反相 PGA                  |

为 OPAMP 模块选择全局选项后,可以单独设置各个运放。第一个选项是选择所需的配置。每种配置都提供对应的配置图。对于不同的配置,OPAMPn 设置中会有不同的字段呈灰显状态。灰显字段不得更改,否则会破坏配置,这些字段之所以可见是为了显示运放采用何种配置。其他字段可以正常更改,通常用于更改配置的输入或增益。

### 图 3-2. Atmel START 运放配置

最后几个选项("HARDWARE SETTINGS"(硬件设置))是每个运放特定的硬件部分,默认配置为始终开启以及处于正常输出模式。这样,运放可在初始化后立即工作。稳定时间设置为最大值,因为这是在未知负载情况下的推荐值。

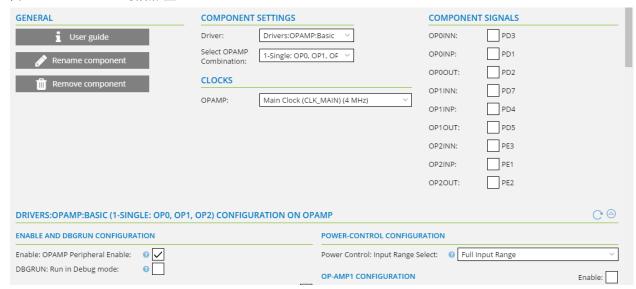

## 4. MPLAB® X MCC

MPLAB® X MCC 带有 OPAMP 模块的驱动程序,可轻松配置该模块。MCC 模块具有 9 种预定义配置以及自定义模式。

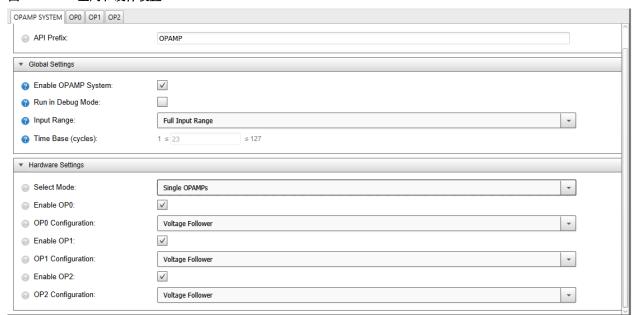

## 图 4-1. MCC 全局和硬件设置

在"OPAMP SYSTEM"(OPAMP 系统)选项卡下(如图 4-1 所示),可以为模块设置几个全局选项,例如使能模块,在调试模式下使能模块,以及选择输入范围。在"Hardware Settings"下,选择模式选项用于选择运放采用单独配置还是组合构成多运放配置。所有运放都可以采用任何单运放配置,但某些多运放配置仅适用于特定的运放。有关可能组合的概述,请参见表 4-1。

表 4-1. 多运放配置

| 运放组合        | 可能的配置                           |

|-------------|---------------------------------|

| OP1-OP2     | 差分放大器,级联(两个)同相 PGA,级联(两个)反相 PGA |

| OP2-OP1     | 差分放大器,级联(两个)同相 PGA,级联(两个)反相 PGA |

| OP2-OP0     | 差分放大器,级联(两个)反相 PGA              |

| OP0-OP1-OP2 | 仪表放大器,级联(三个)同相 PGA,级联(三个)反相 PGA |

| OP1-OP2-OP0 | 仪表放大器,级联(三个)反相 PGA              |

| OP2-OP0-OP1 | 仪表放大器,级联(三个)反相 PGA              |

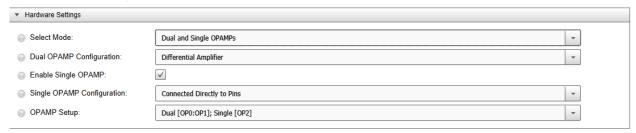

如果选择 *Single OPAMP*(单 OPAMP)选项,每个运放都可以单独使能和配置,如图 **4-1** 所示。如果选择 *Dual and Single OPAMP*s(双 OPAMP 和单 OPAMP)或 *Triple OPAMP*s(三 OPAMP)选项,则可选择双 OPAMP 或三 OPAMP 配置。图 **4-2** 给出了单运放的配置(如果存在)以及运放应采用的连接方式。

#### 图 4-2. 双 OPAMP 和单 OPAMP 配置

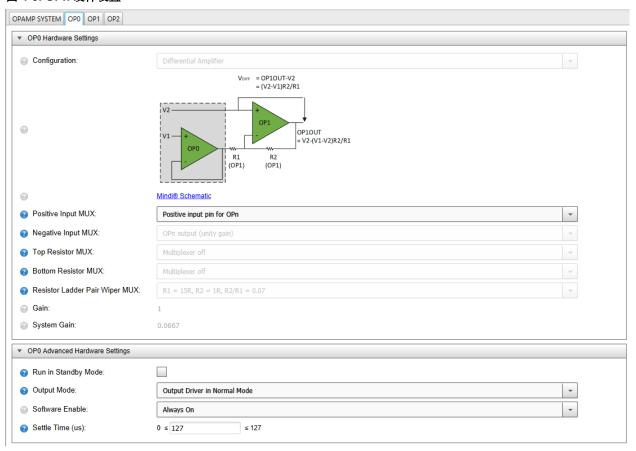

选择全局选项和硬件设置后,每个已使能的运放都会有一个对应的选项卡,可以在其中选择运放特定的选项。每种配置都提供对应的配置图。对于不同的配置,"OP0 Hardware Settings"(OP0 硬件设置)中会有不同的字段呈灰显状态。灰显字段不得更改,否则会破坏配置,这些字段之所以可见是为了显示运放采用何种配置。其他字段可以正常更改,通常用于更改配置的输入或增益。

## 图 4-3. OPn 硬件设置

最后几个选项位于"OPn Advanced Hardware Settings"(OPn 高级硬件设置)下,默认配置为始终开启以及处于正常输出模式。这样,运放可在初始化后立即工作。稳定时间设置为最大值,因为这是在未知负载情况下的推荐值。

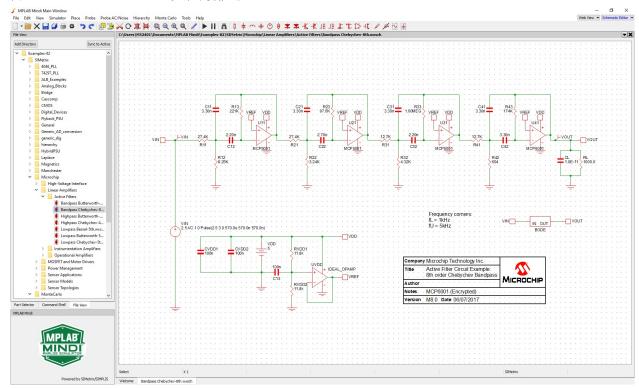

## 5. MPLAB® Mindi™模拟仿真器

仿真电子电路可以减少设计迭代,从而节省开发时间和资源。在早期阶段即可发现代价高昂的设计错误并轻松予以纠正。仿真还具备重要的学习能力,可以快速表征和理解电路的工作原理。

MPLAB Mindi 模拟仿真器是一款用于模拟电路设计和分析的综合性工具。该工具使用 SIMetrix/SIMPLIS 仿真环境,可满足非常广泛的仿真需求。操作界面简单易用,仿真速度快,模型库与应用原理图也在日益完备。可用的模型库包括:运算放大器、有源滤波器电路、MOSFET 和电机驱动器、电源模块、LED 驱动器、开关稳压器、通用开关和无源元件。

MPLAB Mindi 在本地安装和运行。下载后无需联网,仿真运行时不依赖于远程服务器。因此,仿真模拟电路时既快速 又准确。可从 MPLAB Mindi 中极大受益的应用包括:

- · 为有源和无源滤波器系统生成 BODE 响应

- 评估对各种输入条件的瞬态响应

- 生成控制系统的闭环稳定性响应

- 通过电源驱动或信号调理链验证压摆率和驱动能力

- 对信号调理或控制系统中的噪声影响进行建模

#### 图 5-1. MPLAB® Mindi™——设计环境概述

最新版 MPLAB Mindi 可在 MPLAB Mindi 模拟仿真器产品页面下载。

前文所述的每种拓扑均有对应的 Mindi 原理图和仿真,通过一个简单的示例展示配置。在目标器件中编程固件后功能硬件配置的预期结果也将以此为前提。

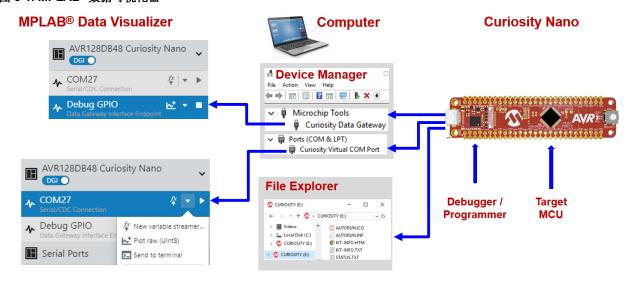

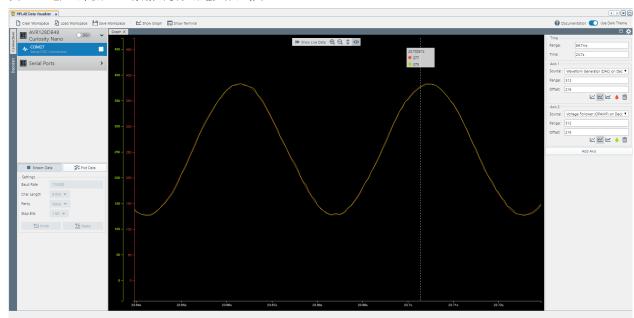

## 6. MPLAB 数据可视化器

MPLAB 数据可视化器是一款用于对正在运行的嵌入式目标的关键数据点进行实时处理和可视化的程序。该实用程序既可作为 MPLAB X IDE 插件访问,也可作为独立程序访问。最新版 MPLAB 数据可视化器可在 MPLAB 数据可视化器产品页面下载。

图 6-1 给出了主要概念及功能的概览,例如:

- 通过虚拟串行端口(USB)或数据网关接口(Data Gateway Interface,DGI)捕捉来自正在运行的嵌入式目标的数据

- 在运行时使用数据流协议格式解码数据字段

- 将图表中的原始或解码数据以时间序列的形式显示,或在终端中显示数据

- 传输数据的同时调试目标代码

### 图 6-1. MPLAB®数据可视化器

每种配置均设置为将数据作为*数据可视化器数据流*通过 USART 发送。相关值为输入和输出信号。这两个信号均将显示在 MPLAB *数据可视化器*的主 *Graph*(图表)区域。接口和基本设置通过名为 *data-visualizer* 的文件夹中提供的已保存工作区进行配置。

要启动并运行工作区,请按照以下步骤操作:

注: 没有可用于简单 OPAMP 项目的 MPLAB 数据可视化器工作区。

- 1. 导航到 GitHub 资源库并选择 Getting\_Started\_with\_OPAMP.atsIn,打开 Atmel Studio 7 解决方案 Getting\_Started\_with\_OPAMP。该解决方案包含本文档中详述的所有配置对应的项目。

- 2. 右键单击所需项目并从弹出菜单中选择 Set as StartUp Project (设置为启动项目)选项,将该项目设置为*启动项目*。

### 图 6-2. Atmel Studio 7——设置启动项目

- 3. 选择 Build → Build Solution (编译 → 编译解决方案) 或按下 F7,编译解决方案。

- 4. 从顶部菜单栏选择 Debug → Start Without Debugging (调试 → 无需调试直接开始),编程 AVR DB 器件。

- 5. 打开 MPLAB 数据可视化器。

- 6. 加载工作区。接下 *Load Workspace*(加载工作区)接钮并添加与配置对应的工作区文件(在 **GitHub** 资源库中提供)。图表中应出现两个轴。

- 7. 设置正确的串行端口设置。在左侧面板上选择 COM 端口(如图 6-3 所示)。确保 Baud Rate(波特率)为 115200,然后按下播放按钮(Fhackappa 3 。

## 图 6-3. MPLAB 数据可视化器——串行端口设置

8. 确保选择 COM 端口作为 Variable Streamer Decoder 的源。

#### 图 6-4. MPLAB 数据可视化器——Variable Streamers

- 9. 如果成功,屏幕上将绘制两条分别代表输入和输出信号的曲线图。Y 轴代表以 mV 为单位的信号幅值,而 X 轴代表经过的时间。

- 注: 有关 MPLAB 数据可视化器的更多信息,请参见相关文档资源。

## 7. 运放基本配置

图 7-1 所示为运放直接连接到器件引脚的情况。运放的输入和输出未连接到内部反馈电阻网络。

#### 图 7-1. 运放直接连接到 I/O 引脚

## 7.1 用例

如果用户希望在外部与其他元件建立所有连接,该配置会十分有用。当需要模拟比较功能时(在一些特定情况下),应使用专门为此类应用构建的独立模拟比较器模块。

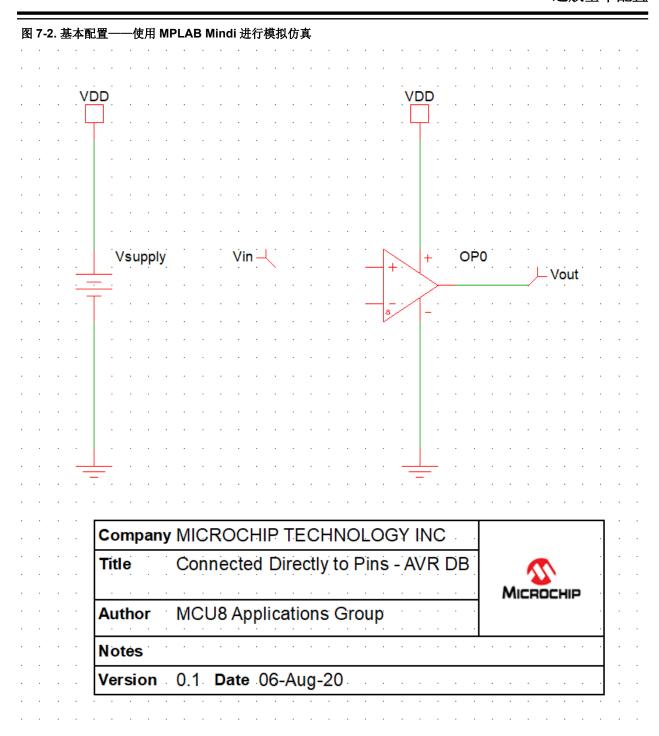

## 7.2 MPLAB Mindi 模型

在 MPLAB Mindi 中仿真的运放均使用 AVR DB 数据手册中提供的电气直流和交流特性中的参数创建。

在 MPLAB Mindi 中,打开来自 GitHub 资源库的 opamp.wxsch 原理图。

图 7-2 所示的电路仅包含运放,无任何外部元件,因此可通过连接适当的外部元件实现任何标准运放配置。

选择 Simulator → Run Schematic (仿真器 → 运行原理图) 或**按下功能键 F9** 进行仿真。

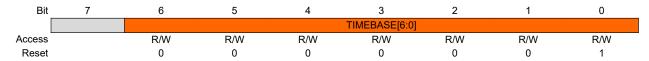

## 7.3 寄存器配置

必须先配置模拟信号调理(OPAMP)外设的时基寄存器。用户必须编程相当于  $1 \mu s$  的时钟周期数,以使内容取决于 CPU 的工作时钟频率。

### 图 7-3. OPAMP.TIMEBASE——设置时基

#### Bits 6:0 - TIMEBASE[6:0] Timebase

This bit field controls the maximum value of a counter that counts CLK\_PER cycles to achieve a time interval equal to or larger than 1 µs. It should be written with one less than the number of CLK\_PER cycles that are equal to or larger than 1 µs. This is used for internal timing of the warmup and settling times.

```

#define OPAMP_TIMEBASE_US (ceil(F_CPU /1e6)-1)

OPAMP.TIMEBASE = OPAMP_TIMEBASE_US;

```

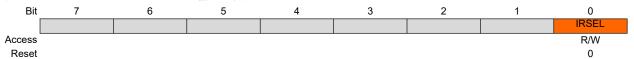

在不需要轨到轨输入电压范围的应用中,可通过向电源控制(PWRCTRL)寄存器中的输入范围选择(IRSEL)位写入 1 将 OPAMP 外设配置为节能模式。对于本技术简介中的基本运放应用,将不会使用节能选项。

#### 图 7-4. OPAMP.PWRCTRL——设置输入范围

#### Bit 0 - IRSEL Input Range Select

This bit selects the op amp input voltage range

| Value | Description                                                                          |

|-------|--------------------------------------------------------------------------------------|

| 0     | The op amp input voltage range is rail-to-rail                                       |

| 1     | The op amp input voltage range and power consumption are reduced. See the Electrical |

|       | Characteristics section for more information                                         |

OPAMP.PWRCTRL = OPAMP PWRCTRL IRSEL FULL gc;

对于基本运放配置操作,运放配置为始终开启,前提是这种情况下未使用 ENABLE/DISABLE 事件来使能/禁止运放。同样地,通过选择正常输出模式来使能输出驱动器。不过,在不同的应用中,可基于特定事件发生器(TCA、TCB、TCD、RTC、PORT 和 CCL 等)使能或禁止运放。此功能有助于实现节能,即让运放仅在需要时使能,而非从电路上电后便一直使能。

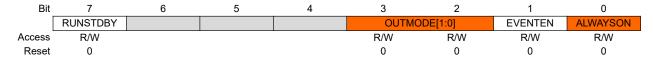

## 图 7-5. OPAMP.OPnCTRLA——配置运放控制 A

## Bit 7 - RUNSTDBY Run in Standby Mode

This bit controls whether or not the op amp functions in Standby sleep mode.

|       | , , , , , , , , , , , , , , , , , , ,                                          |

|-------|--------------------------------------------------------------------------------|

| Value | Description                                                                    |

| 0     | OPn is disabled when in Standby sleep mode, and its output driver is disabled. |

| 1     | OPn will continue operating as configured in Standby sleep mode.               |

## Bits 3:2 - OUTMODE[1:0] Output Mode

This bit field selects the output mode of the output driver.

| Value | Name   | Description                                                                            |

|-------|--------|----------------------------------------------------------------------------------------|

| 0x0   | OFF    | The output driver for OPn is disabled, but this can be overridden by the DRIVEn event. |

| 0x1   | NORMAL | The output driver for OPn is enabled in Normal mode.                                   |

| 0x2 - | -      | Reserved                                                                               |

| 0x3   |        |                                                                                        |

#### Bit 1 - EVENTEN Event Enable

This bit enables event reception and generation.

| Mala  |                                 |

|-------|---------------------------------|

| value | Description                     |

| 0     | No events are enabled for OPn.  |

| 1     | All events are enabled for OPn. |

#### Bit 0 - ALWAYSON Always On

This bit controls whether the op amp is always on or not.

| Value | Description                                                                                |

|-------|--------------------------------------------------------------------------------------------|

| 0     | OPn is not always on, but can be enabled by the ENABLEn event and disabled by the DISABLEn |

|       | event.                                                                                     |

| 1     | OPn is always on.                                                                          |

OPAMP.OPOCTRLA = OPAMP OPOCTRLA OUTMODE NORMAL gc | OPAMP ALWAYSON bm;

对于基本运放操作,运放的输入和输出直接连接到器件的引脚。实现基本运放配置所需的多路开关设置如下:

#### 表 7-1. 运放直接连接到引脚

|     | MUXPOS | MUXNEG | михвот | MUXWIP | MUXTOP |

|-----|--------|--------|--------|--------|--------|

| OPn | INP    | INN    | OFF    | WIP0   | OFF    |

对于基本运放配置,梯形电阻网络配置将保持为 0x00。

## 图 7-6. OPAMP.OPnRESMUX——配置梯形电阻网络多路开关

| Bit    | 7           | 6   | 5   | 4           | 3   | 2   | 1           | 0   |

|--------|-------------|-----|-----|-------------|-----|-----|-------------|-----|

|        | MUXWIP[2:0] |     |     | MUXBOT[2:0] |     |     | MUXTOP[1:0] |     |

| Access | R/W         | R/W | R/W | R/W         | R/W | R/W | R/W         | R/W |

| Reset  | 0           | 0   | 0   | 0           | 0   | 0   | 0           | 0   |

Bits 7:5 - MUXWIP[2:0] Multiplexer for Wiper

This bit field selects the resistor ladder wiper (potentiometer) position.

| Value | Name | Description       |

|-------|------|-------------------|

| 0x0   | WIP0 | R1 = 15R, R2 = 1R |

| 0x1   | WIP1 | R1 = 14R, R2 = 2R |

| 0x2   | WIP2 | R1 = 12R, R2 = 4R |

| 0x3   | WIP3 | R1 = 8R, R2 = 8R  |

| 0x4   | WIP4 | R1 = 6R, R2 = 10R |

| 0x5   | WIP5 | R1 = 4R, R2 = 12R |

| 0x6   | WIP6 | R1 = 2R, R2 = 14R |

| 0x7   | WIP7 | R1 = 1R, R2 = 15R |

## Bits 4:2 - MUXBOT[2:0] Multiplexer for Bottom

This bit field selects the analog signal connected to the bottom resistor in the resistor ladder.

| Value | Name    | Description                                                    |

|-------|---------|----------------------------------------------------------------|

| 0x0   | OFF     | Multiplexer off                                                |

| 0x1   | INP     | Positive input pin for OPn                                     |

| 0x2   | INN     | Negative input pin for OPn                                     |

| 0x3   | DAC     | DAC output (DAC and DAC output buffer must be enabled)         |

| 0x4   | LINKOUT | OP[n-1] output (Setting only available for OP1) <sup>(1)</sup> |

| 0x5   | GND     | Ground                                                         |

| Other | -       | Reserved                                                       |

Note: When selecting LINKOUT for OP0, MUXBOT is connected to the output of OP2.

### Bits 1:0 - MUXTOP[1:0] Multiplexer for Top

This bit field selects the analog signal connected to the top resistor in the resistor ladder.

| Value | Name | Description     |

|-------|------|-----------------|

| 0x0   | OFF  | Multiplexer off |

| 0x1   | OUT  | OPn output      |

| 0x2   | VDD  | $V_{DD}$        |

| Other | -    | Reserved        |

OPAMP.OPORESMUX = OPAMP\_OPORESMUX\_MUXBOT\_OFF\_gc | OPAMP\_OPORESMUX\_MUXWIP\_WIPO\_gc | OPAMP\_OPORESMUX\_MUXTOP\_OFF\_gc;

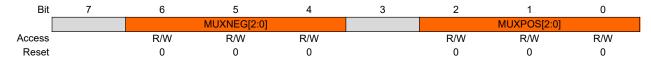

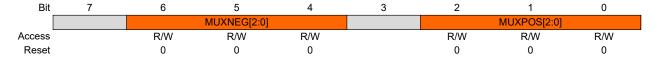

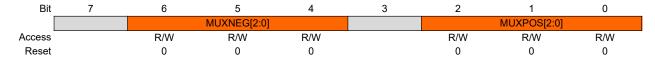

运放的反相输入和同相输入直接连接到 I/O 引脚。

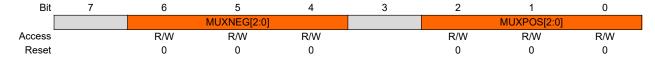

## 图 7-7. OPAMP.OPnINMUX——配置输入多路开关

### Bits 6:4 - MUXNEG[2:0] Multiplexer for Negative Input

This bit field selects which analog signal is connected to the inverting (-) input of OPn.

|       |      | 3 7 1                                                  |

|-------|------|--------------------------------------------------------|

| Value | Name | Description                                            |

| 0x0   | INN  | Negative input pin for OPn                             |

| 0x1   | WIP  | Wiper from OPn's resistor ladder                       |

| 0x2   | OUT  | OPn output (unity gain)                                |

| 0x3   | DAC  | DAC output (DAC and DAC output buffer must be enabled) |

| Other | -    | Reserved                                               |

#### Bits 2:0 - MUXPOS[2:0] Multiplexer for Positive Input

This bit field selects which analog signal is connected to the non-inverting (+) input of OPn.

| Value | Name    | Description                                                       |

|-------|---------|-------------------------------------------------------------------|

| 0x0   | INP     | Positive input pin for OPn                                        |

| 0x1   | WIP     | Wiper from OPn's resistor ladder                                  |

| 0x2   | DAC     | DAC output (DAC and DAC output buffer must be enabled)            |

| 0x3   | GND     | Ground                                                            |

| 0×4   | VDDDIV2 | $V_{\mathrm{DD/2}}$                                               |

| 0x5   | LINKOUT | OP[n-1] output (Setting only available for OP1 and OP2)           |

| 0x6   | LINKWIP | Wiper from OP0's resistor ladder (Setting only available for OP2) |

| Other | -       | Reserved                                                          |

OPAMP.OPOINMUX = OPAMP OPOINMUX MUXNEG INN gc | OPAMP OPOINMUX MUXPOS INP gc;

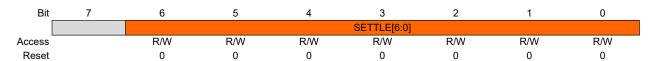

稳定时间取决于多种因素(包括运放上的负载),直到设计和开发的后期阶段才能确定。如果稳定时间未知,应将最大值  $0 \times 7 F$ (127  $\mu s$ )写入 SETTLE 位域。

## 图 7-8. OPAMP.OPnSETTLE——配置稳定时间

#### Bits 6:0 - SETTLE[6:0] Settle Time

This bit field specifies the number of microseconds allowed for the op amp output to settle. This value is used by an internal timer to determine when to generate the READYn event and set the SETTLED flag in the OPnSTATUS register.

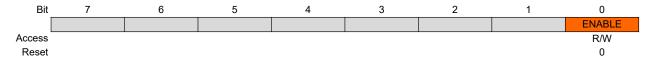

通过将 OPAMP.CTRLA 寄存器中的 ENABLE 位置 1 来使能运算放大器模块。

## 图 7-9. OPAMP.CTRLA——使能 OPAMP 外设

#### Bit 0 - ENABLE Enable OPAMP Peripheral

This bit controls whether the OPAMP peripheral is enabled or not.

| Value | Description                       |

|-------|-----------------------------------|

| 0     | The OPAMP peripheral is disabled. |

| 1     | The OPAMP peripheral is enabled.  |

OPAMP.CTRLA = OPAMP\_ENABLE\_bm;

及其子公司

SETTLED 位的值为 0 表示稳定时间已过:

#### 图 7-10. OPAMP.OPOSnATUS——OPAMP 状态

```

Bit 7 6 5 4 3 2 1 0

SETTLED

Access

Reset

0

```

#### Bit 0 - SETTLED Op Amp has Settled

This bit is cleared when the op amp is waiting for settling time related to enabling or configuration changes. This bit is set when the allowed settling time is finished.

```

while (OPAMP.OPOSTATUS & OPAMP_SETTLED_bm)

{

;

}

```

将上述代码组合在一起就是基本运放的初始化代码,具体如下所示:

```

void OPAMPO_init (void)

/*配置时基*/

OPAMP.TIMEBASE = OPAMP_TIMEBASE_US;

/*配置电压输入范围*/

OPAMP.PWRCTRL = OPAMP PWRCTRL IRSEL FULL gc;

/*配置运放 n 控制 A */

OPAMP.OPOCTRLA = OPAMP_OPOCTRLA_OUTMODE_NORMAL_gc | OPAMP_ALWAYSON_bm;

/*配置运放 n 输入多路开关*/

OPAMP.OP0INMUX = OPAMP OP0INMUX MUXNEG INN gc | OPAMP OP0INMUX MUXPOS INP gc;

/*配置运放 n 电阻抽头多路开关*/

OPAMP.OPORESMUX = OPAMP OPORESMUX MUXBOT OFF gc | OPAMP OPORESMUX MUXWIP WIPO gc |

OPAMP_OPORESMUX_MUXTOP_OFF_gc;

/*配置运放 n 稳定时间*/

OPAMP.OPOSETTLE = 0x7F;

/*使能 OPAMP 外设*/

OPAMP.CTRLA = OPAMP ENABLE bm;

/*等待运算放大器稳定*/

while (OPAMP.OPOSTATUS & OPAMP SETTLED bm)

{

}

```

本示例的代码可从以下 GitHub 资源库中的 simple-opamp 文件夹获取。

注: 本示例不适用于 Atmel START 或 MPLAB® X MCC。

## 8. 电压跟随器

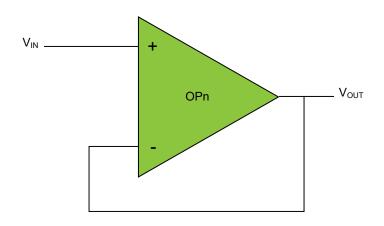

图 8-1 所示为运放的电压跟随器配置,也称为单位增益缓冲器或电压缓冲器。同相(+)输入连接到引脚,输出连接到反相(-)输入。

#### 图 8-1. 电压跟随器

输出电压等于输入电压,对应的传递函数如下:

$$V_{OUT} = V_{IN}$$

该配置不提供任何放大,因此电压增益等于1。

电压跟随器主要用于将高输入阻抗转换为低输出阻抗,经常在采样保持电路中作为模数转换器(ADC)的输入或逻辑电路的缓冲器。

## 8.1 用例

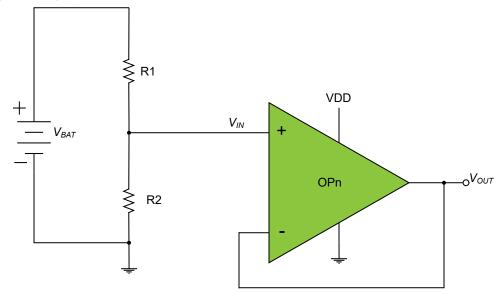

在电池供电的电子产品中,经常会使用电池监视系统(Battery Monitoring System,BMS)IC。这类元件会在非常基本的层面上持续测量电池电压和负载电流。利用这些信息,可以计算出电池何时需要充电或更换,以便在设备因断电无法使用之前通知用户。

对于成本敏感型设备,基于分压器和运算放大器的解决方案可能会比较划算(见图 8-2)。电压缓冲器的输入是电池电压的比率,而电压缓冲器的输出可以在内部连接到 ADC 以进行采集和进一步处理。

$$V_{OUT} = \frac{R_2}{R_1 + R_2} \times V_{BAT}$$

为了最大程度地降低电流消耗,应选择较高的电阻值(有关典型值,请参见表 8-1)。这种设计选择通常会给单片机的 ADC 带来挑战。因为 ADC 输入通常不进行缓冲,所以 ADC 的输入电流往往会导致测量误差。此时引入电压跟随器/缓冲器可以调整分压器输出的高阻抗,以此适应 ADC 输入的低阻抗。

图 8-2. 外部电池电压缓冲器

在这种设计中,电池电压独立于运放电源轨(通常是这种情况)。电池电压通过由 R1 和 R2 构成的分压器控制在放大器的共模输入电压范围内。对于 2S1P 锂离子电池组,安全工作电压可以是 5V 和 8.4V 之间的任何值。但是,MCU 的电源电压稳压在 3V。当分压器的 R2 与 R1 之比为 1:8.66 时,监视电压介于 0.5V 和 0.87V 之间(见上面的电压传递函数)。可以选择内部 1.024V 带隙参考电压作为 ADC 的参考电压。

为了最大程度地降低电流消耗并减少其对电池寿命的影响,务必为分压器选择合适的电阻值。 表 8-1 简要说明了分压器电阻值的影响,并未考虑任何潜在负载,例如单片机的工作电流。最终得出的电池寿命值均以下列条件为前提: 设计在近乎理想的环境下工作,锂离子电池的标称电压为 3.7V/节,自放电量为容量的 20%。

表 8-1. 分压器——选择合适的电阻值以实现低功耗

| 电阻分压值   |      | 电流消耗                    | 给定电池容量的电池寿命 |          |

|---------|------|-------------------------|-------------|----------|

| R1      | R2   | V <sub>BAT</sub> = 7.4V | 1650 mAh    | 2950 mAh |

| 8.66 kΩ | 1 kΩ | 0.76 mA                 | 约71天        | 约 128 天  |

| 8.66 MΩ | 1 ΜΩ | 0.76 μΑ                 | 约 198 年     | 约 351 年  |

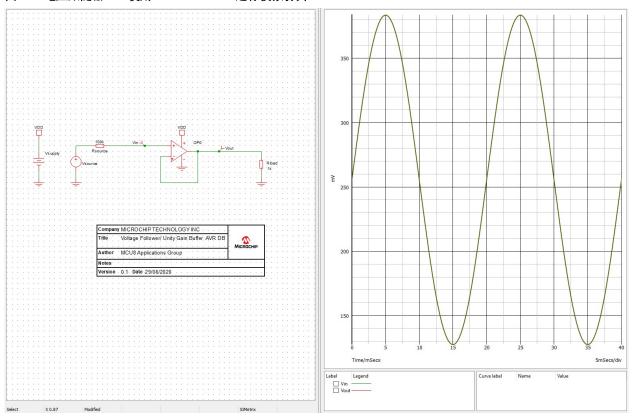

## 8.2 使用 MPLAB Mindi 进行电压跟随器模拟仿真

在 MPLAB Mindi 中,打开来自 GitHub 资源库的 Voltage\_Follower.wxsch 原理图。

图 8-3 左半部分所示电路由具有 256 mV 直流失调的 50 Hz、256 mV<sub>PP</sub> 正弦信号源驱动。运放由 5V 电池供电。

## 图 8-3. 电压跟随器——使用 MPLAB Mindi 进行模拟仿真

选择 Simulator → Run Schematic 或按下功能键 F9 进行仿真。最终得到的仿真输出曲线图如图 8-3 的右半部分所示。可以看到,输出信号紧随输入信号之后。这恰好符合电压跟随器应用的预期。

## 8.3 寄存器配置

上一节简要介绍了电压跟随器电路的 MPLAB Mindi 仿真。本节将配置相关 AVR DB OPAMP 寄存器以使能电压跟随器配置及操作。有两种选择:

- 运放的同相输入连接到器件的输入引脚

- 运放的同相输入在内部连接到数模转换器(Digital-to-Analog Converter,DAC)的输出。随附的代码示例中使用该配置。

表 8-2. 电压跟随器的同相输入连接到器件引脚

|     | MUXPOS | MUXNEG | MUXBOT | MUXWIP | MUXTOP |

|-----|--------|--------|--------|--------|--------|

| OPn | INP    | OUT    | OFF    | WIP0   | OFF    |

表 8-3. 电压跟随器的同相输入连接到内部 DAC

|     | MUXPOS | MUXNEG | михвот | MUXWIP | MUXTOP |

|-----|--------|--------|--------|--------|--------|

| OPn | DAC    | OUT    | OFF    | WIP0   | OFF    |

对于电压跟随器,梯形电阻网络多路开关寄存器将保持配置为 0x00。

## 图 8-4. OPAMP.OPnRESMUX——配置梯形电阻网络多路开关

| Bit    | 7           | 6   | 5   | 4           | 3   | 2   | 1           | 0   |

|--------|-------------|-----|-----|-------------|-----|-----|-------------|-----|

|        | MUXWIP[2:0] |     |     | MUXBOT[2:0] |     |     | MUXTOP[1:0] |     |

| Access | R/W         | R/W | R/W | R/W         | R/W | R/W | R/W         | R/W |

| Reset  | 0           | 0   | 0   | 0           | 0   | 0   | 0           | 0   |

Bits 7:5 - MUXWIP[2:0] Multiplexer for Wiper

This bit field selects the resistor ladder wiper (potentiometer) position.

| Value | Name | Description       |

|-------|------|-------------------|

| 0x0   | WIP0 | R1 = 15R, R2 = 1R |

| 0x1   | WIP1 | R1 = 14R, R2 = 2R |

| 0x2   | WIP2 | R1 = 12R, R2 = 4R |

| 0x3   | WIP3 | R1 = 8R, R2 = 8R  |

| 0x4   | WIP4 | R1 = 6R, R2 = 10R |

| 0x5   | WIP5 | R1 = 4R, R2 = 12R |

| 0x6   | WIP6 | R1 = 2R, R2 = 14R |

| 0x7   | WIP7 | R1 = 1R, R2 = 15R |

## Bits 4:2 - MUXBOT[2:0] Multiplexer for Bottom

This bit field selects the analog signal connected to the bottom resistor in the resistor ladder.

| Value | Name    | Description                                                    |

|-------|---------|----------------------------------------------------------------|

| 0x0   | OFF     | Multiplexer off                                                |

| 0x1   | INP     | Positive input pin for OPn                                     |

| 0x2   | INN     | Negative input pin for OPn                                     |

| 0x3   | DAC     | DAC output (DAC and DAC output buffer must be enabled)         |

| 0x4   | LINKOUT | OP[n-1] output (Setting only available for OP1) <sup>(1)</sup> |

| 0x5   | GND     | Ground                                                         |

| Other | -       | Reserved                                                       |

Note: When selecting LINKOUT for OP0, MUXBOT is connected to the output of OP2.

Bits 1:0 - MUXTOP[1:0] Multiplexer for Top

This bit field selects the analog signal connected to the top resistor in the resistor ladder.

| Value | Name | Description     |

|-------|------|-----------------|

| 0x0   | OFF  | Multiplexer off |

| 0x1   | OUT  | OPn output      |

| 0x2   | VDD  | $V_{DD}$        |

| Other | -    | Reserved        |

OPAMP\_OPORESMUX = OPAMP\_OPORESMUX\_MUXBOT\_OFF\_gc | OPAMP\_OPORESMUX\_MUXWIP\_WIPO\_gc | OPAMP\_OPORESMUX\_MUXTOP\_OFF\_gc;

在本文档随附的电压跟随器代码示例中,运放的输出连接到反相输入。运放的同相输入在内部连接到 DAC 输出。

### 图 8-5. OPAMP.OPnINMUX——配置输入多路开关

Bits 6:4 - MUXNEG[2:0] Multiplexer for Negative Input

This bit field selects which analog signal is connected to the inverting (-) input of OPn.

| Value | Name | Description                                            |

|-------|------|--------------------------------------------------------|

| 0x0   | INN  | Negative input pin for OPn                             |

| 0x1   | WIP  | Wiper from OPn's resistor ladder                       |

| 0x2   | OUT  | OPn output (unity gain)                                |

| 0x3   | DAC  | DAC output (DAC and DAC output buffer must be enabled) |

| Other | -    | Reserved                                               |

#### Bits 2:0 - MUXPOS[2:0] Multiplexer for Positive Input

This bit field selects which analog signal is connected to the non-inverting (+) input of OPn.

| Value | Name    | Description                                                       |

|-------|---------|-------------------------------------------------------------------|

| 0x0   | INP     | Positive input pin for OPn                                        |

| 0x1   | WIP     | Wiper from OPn's resistor ladder                                  |

| 0x2   | DAC     | DAC output (DAC and DAC output buffer must be enabled)            |

| 0x3   | GND     | Ground                                                            |

| 0x4   | VDDDIV2 | $V_{DD/2}$                                                        |

| 0x5   | LINKOUT | OP[n-1] output (Setting only available for OP1 and OP2)           |

| 0x6   | LINKWIP | Wiper from OP0's resistor ladder (Setting only available for OP2) |

| Other | -       | Reserved                                                          |

```

OPAMP.OPOINMUX = OPAMP_OPOINMUX_MUXNEG_OUT_gc | OPAMP_OPOINMUX_MUXPOS_DAC_gc;

```

电压跟随器初始化代码如下所示:

```

void OPAMPO init (void)

/*配置时基*/

OPAMP.TIMEBASE = OPAMP TIMEBASE US;

/*配置电压输入范围*/

OPAMP.PWRCTRL = OPAMP PWRCTRL IRSEL FULL gc;

/*配置运放 n 控制 A */

OPAMP.OPOCTRLA = OPAMP_OPOCTRLA_OUTMODE_NORMAL_gc | OPAMP_ALWAYSON_bm;

/*配置运放 n 输入多路开关*/

OPAMP.OPOINMUX = OPAMP_OPOINMUX_MUXNEG_OUT_gc | OPAMP_OPOINMUX_MUXPOS_DAC_gc;

/*配置运放 n 电阻抽头多路开关*/

OPAMP.OPORESMUX = OPAMP_OPORESMUX_MUXBOT_OFF_gc | OPAMP_OPORESMUX_MUXWIP_WIPO_gc | OPAMP_OPORESMUX_MUXTOP_OFF_gc;

/*配置运放 n 稳定时间*/

OPAMP.OPOSETTLE = 0x7F;

/*使能 OPAMP 外设*/

OPAMP.CTRLA = OPAMP ENABLE bm;

/*等待运算放大器稳定*/

while (OPAMP.OPOSTATUS & OPAMP_SETTLED_bm)

{

}

```

本示例的代码可从以下 GitHub 资源库中的 voltage-follower 文件夹获取。

## 8.4 以数据形式传输到 MPLAB 数据可视化器

本节将使用 Curiosity Nano 上的 AVR DB 的内部运放之一演示此类操作。因此,将为单片机编程应用程序以执行以下操作:

- 将 OPAMP0 配置为电压跟随器

- 使用片上 DAC 和 TCB0 产生 50 Hz 正弦波, 然后馈入 OPAMP0 的同相输入

- 采用片上 TCB1 和 ADC 对 OPAMP0 的输出进行采样

- 将 ADC 结果和 DAC 采样以数据形式通过 USART 传输到 MPLAB 数据可视化器

该应用程序对硬件没有要求,因为所有上述模块和连接均在 AVR DB 内部。

要启动并运行演示,请按照 6. MPLAB 数据可视化器所述步骤操作。要加载的工作区文件是 *voltage\_follower.json*,可在 GitHub 资源库中获取。 图 8-6 所示为预期结果示例。

#### 图 8-6. 电压跟随器——数据可视化器输出曲线图

在该曲线图中,红色表示 DAC 波形,绿色表示配置为电压跟随器的 OPAMP0 的采样输出。正如仿真步骤所预期的那样,两个信号在幅值和时间上发生重叠。DAC 产生的波形与 ADC 采样的波形之间存在信号幅值差异,这是由于与 DAC、ADC 和运放相关的累积误差所致(此类讨论超出了本文档的范围)。

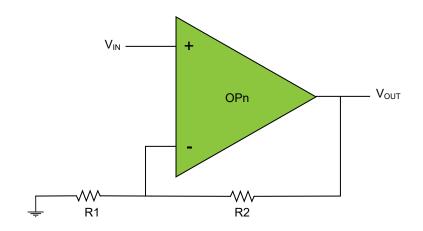

## 9. 同相可编程增益放大器

图 9-1 所示为运放的同相放大器配置。与之前的电压跟随器配置的主要区别在于负反馈环中存在 R2/R1 电阻分压器。电阻分压器可调大输入信号。这种调节可通过编程 R2/R1 比来完成,因此称为可编程增益放大器(Programmable Gain Amplifier,PGA)。

#### 图 9-1. 同相可编程增益放大器

输出电压的计算公式如下:

$$V_{OUT} = \left(1 + \frac{R_2}{R_1}\right) V_{IN}$$

配置增益(放大)的计算公式如下:

$$Gain = 1 + \frac{R_2}{R_1}$$

与电压跟随器的情况一样,同相可编程增益放大器适用于将高输入阻抗与低输出阻抗耦合,非常适合作为耦合到 ADC 的低压信号之间的中间级。

## 9.1 用例

同相放大器(如上一节所述)的优势在于能够:

- 将高阻抗信号源耦合到低阻抗信号阱

- 获取输入信号并将其放大一定倍数,即 *G (增益)*。增益与反馈环中的 R2/R1 电阻值比成正比(见图 9-1)。

这两个属性使得同相放大器成为了 ADC 预输入级的理想选择,原因有以下两点:

- ADC 的输入阻抗值较低,因此同相放大器充当缓冲器

- 扩大了输入信号的动态范围,从而提高采样分辨率

假设存在这种情形: ADC 输入信号相对于系统地为 25 mV。ADC 的分辨率为 10 位,参考电压选定为 1.024V。这意味着,按照数据手册所述,一个最低有效位(Least Significant bit,LSb)的量化误差相当于 1 mV,即输入信号的 4%。如果要求测量准确,这会是一个很大的误差源。但如果提前为 ADC 要采样的输入信号进行放大,则可以改善这种情况。当增益为 16 时,输入信号在被采样之前将放大至 400 mV。在这种情况下,1 mV 的量化误差仅为输入信号的 0.25%,这是一个相当大的改善。

在一些应用中,通常会要求同相放大器具有固定增益(通过负反馈环中的外部电阻进行设置)。这类应用假定输入信号将处于一个固定的预定义范围内。但如果输入信号具有高动态范围,或者传感器的输出信号由于外部(例如,环

境)或内部(例如,老化)因素而随时间变化,则这种设置会受到限制。对于此类情况,如果能够在不改变元件的前提下修改放大器的增益,则将会十分有利。无论是增大还是减小增益,都会使目标信号再次回到其指定范围内。这可以通过可编程增益放大器(PGA)来实现,其中的反馈电阻比可以在多个值之间进行调节。这类应用很可能涉及控制环,控制环通过算法不断监视控制信号和反馈信号并能够在需要不同增益时做出决策。PGA的应用非常广泛,例如音频和语音、数据采集、工业和医疗仪器、照明、电机控制、电源控制和测试设备。

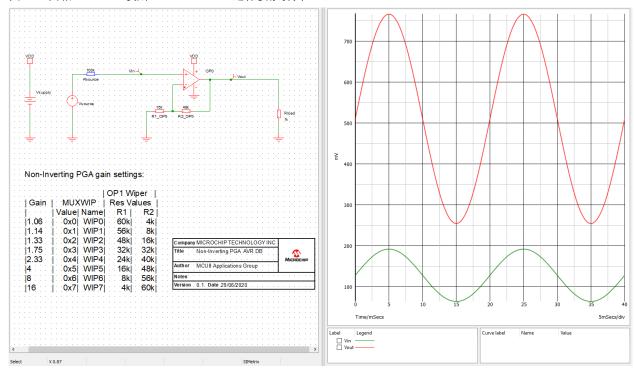

## 9.2 使用 MPLAB Mindi 进行同相 PGA 模拟仿真

在 MPLAB Mindi 中,打开来自 GitHub 资源库的 Non\_Inverting\_PGA(AVR\_DB).wxsch 原理图。

图 9-2 左半部分所示电路由具有 128 mV 直流失调的 50 Hz、128 mV<sub>PP</sub> 正弦信号源驱动。运放由 3.3V 电池电源供电。

### 图 9-2. 同相 PGA——使用 MPLAB Mindi 进行模拟仿真

选择 Simulator → Run Schematic 或按下功能键 F9 进行仿真。最终得到的仿真输出曲线图如图 9-2 的右半部分所示。可以看到,输出信号(红色)是输入信号(绿色)的两倍且保持同相。这恰好符合增益放大器配置的预期。

## 9.3 寄存器配置

上一节简要介绍了同相可编程增益放大器电路的 MPLAB Mindi 仿真。本节将配置相关 AVR DB OPAMP 寄存器以使能同相 PGA 配置及操作,具体如下:

- 运放的同相输入连接到内部数模转换器(DAC)的输出

- 运放的反相输入连接到内部梯形电阻网络的抽头位置

- 梯形电阻网络的底部接地。抽头位置决定增益,梯形电阻网络的顶部连接到运放的输出。

表 9-1 总结了将其中一个内部运放设置为同相 PGA 配置所需的设置。

#### 表 9-1. 同相 PGA 的同相输入连接到内部 DAC

|     | MUXPOS | MUXNEG | михвот | MUXWIP | михтор |

|-----|--------|--------|--------|--------|--------|

| OPn | DAC    | WIP    | GND    | 设置决定增益 | OUT    |

对于同相 PGA, 梯形电阻网络多路开关寄存器将配置为 0x75。

## 图 9-3. OPAMP.OPnRESMUX——配置梯形电阻网络多路开关

| Bit    | 7           | 6   | 5   | 4           | 3   | 2   | 1           | 0   |

|--------|-------------|-----|-----|-------------|-----|-----|-------------|-----|

|        | MUXWIP[2:0] |     |     | MUXBOT[2:0] |     |     | MUXTOP[1:0] |     |

| Access | R/W         | R/W | R/W | R/W         | R/W | R/W | R/W         | R/W |

| Reset  | 0           | 0   | 0   | 0           | 0   | 0   | 0           | 0   |

#### Bits 7:5 - MUXWIP[2:0] Multiplexer for Wiper

This bit field selects the resistor ladder wiper (potentiometer) position.

| Value | Name | Description       |

|-------|------|-------------------|

| 0x0   | WIP0 | R1 = 15R, R2 = 1R |

| 0x1   | WIP1 | R1 = 14R, R2 = 2R |

| 0x2   | WIP2 | R1 = 12R, R2 = 4R |

| 0x3   | WIP3 | R1 = 8R, R2 = 8R  |

| 0x4   | WIP4 | R1 = 6R, R2 = 10R |

| 0x5   | WIP5 | R1 = 4R, R2 = 12R |

| 0x6   | WIP6 | R1 = 2R, R2 = 14R |

| 0x7   | WIP7 | R1 = 1R, R2 = 15R |

#### Bits 4:2 - MUXBOT[2:0] Multiplexer for Bottom

This bit field selects the analog signal connected to the bottom resistor in the resistor ladder.

| Value | Name    | Description                                                    |

|-------|---------|----------------------------------------------------------------|

| 0x0   | OFF     | Multiplexer off                                                |

| 0x1   | INP     | Positive input pin for OPn                                     |

| 0x2   | INN     | Negative input pin for OPn                                     |

| 0x3   | DAC     | DAC output (DAC and DAC output buffer must be enabled)         |

| 0x4   | LINKOUT | OP[n-1] output (Setting only available for OP1) <sup>(1)</sup> |

| 0x5   | GND     | Ground                                                         |

| Other | -       | Reserved                                                       |

Note: When selecting LINKOUT for OP0, MUXBOT is connected to the output of OP2.

### Bits 1:0 - MUXTOP[1:0] Multiplexer for Top

This bit field selects the analog signal connected to the top resistor in the resistor ladder.

| Value | Name | Description     |

|-------|------|-----------------|

| 0x0   | OFF  | Multiplexer off |

| 0x1   | OUT  | OPn output      |

| 0x2   | VDD  | $V_{DD}$        |

| Other | -    | Reserved        |

OPAMP\_OPORESMUX = OPAMP\_OPORESMUX\_MUXBOT\_GND\_gc | OPAMP\_OPORESMUX\_MUXWIP\_WIP3\_gc | OPAMP\_OPORESMUX\_MUXTOP\_OUT\_gc;

在本文档随附的同相 PGA 代码示例中,运算放大器的输出通过梯形电阻网络连接到反相输入。运算放大器的同相输入在内部连接到 DAC 输出。

### 图 9-4. OPAMP.OPnINMUX——配置输入多路开关

Bits 6:4 - MUXNEG[2:0] Multiplexer for Negative Input

This bit field selects which analog signal is connected to the inverting (-) input of OPn.

| Value | Name | Description                                            |

|-------|------|--------------------------------------------------------|

| 0x0   | INN  | Negative input pin for OPn                             |

| 0x1   | WIP  | Wiper from OPn's resistor ladder                       |

| 0x2   | OUT  | OPn output (unity gain)                                |

| 0x3   | DAC  | DAC output (DAC and DAC output buffer must be enabled) |

| Other | -    | Reserved                                               |

#### Bits 2:0 - MUXPOS[2:0] Multiplexer for Positive Input

This bit field selects which analog signal is connected to the non-inverting (+) input of OPn.

| Value | Name    | Description                                                       |

|-------|---------|-------------------------------------------------------------------|

| 0x0   | INP     | Positive input pin for OPn                                        |

| 0x1   | WIP     | Wiper from OPn's resistor ladder                                  |

| 0x2   | DAC     | DAC output (DAC and DAC output buffer must be enabled)            |

| 0x3   | GND     | Ground                                                            |

| 0x4   | VDDDIV2 | $V_{\mathrm{DD/2}}$                                               |

| 0x5   | LINKOUT | OP[n-1] output (Setting only available for OP1 and OP2)           |

| 0x6   | LINKWIP | Wiper from OP0's resistor ladder (Setting only available for OP2) |

| Other | -       | Reserved                                                          |

OPAMP.OPOINMUX = OPAMP\_OPOINMUX\_MUXNEG\_WIP\_gc | OPAMP\_OPOINMUX\_MUXPOS\_DAC\_gc;

同相 PGA 初始化代码如下所示:

```

void OPAMPO init (void)

/*配置时基*/

OPAMP.TIMEBASE = OPAMP TIMEBASE US;

/*配置电压输入范围*/

OPAMP.PWRCTRL = OPAMP PWRCTRL IRSEL FULL gc;

/*配置运放 n 控制 A */

OPAMP.OPOCTRLA = OPAMP OPOCTRLA OUTMODE NORMAL gc | OPAMP ALWAYSON bm;

/*配置运放 n 输入多路开关*/

OPAMP.OPOINMUX = OPAMP_OPOINMUX_MUXNEG_WIP_gc | OPAMP_OPOINMUX_MUXPOS_DAC_gc;

/*配置运放 n 电阻抽头多路开关*/

/* WIP3 => R1 = 8R, R2 = 8R */

/*增益 = 1 + R2/R1 = 2 */

OPAMP.OPORESMUX = OPAMP OPORESMUX MUXBOT GND gc | OPAMP OPORESMUX MUXWIP WIP3 gc |

OPAMP_OPORESMUX_MUXTOP_OUT_gc;

/*配置运放 n 稳定时间*/

OPAMP.OPOSETTLE = 0x7F;

/*使能 OPAMP 外设*/

OPAMP.CTRLA = OPAMP ENABLE bm;

/*等待运算放大器稳定*/

while (OPAMP.OPOSTATUS & OPAMP_SETTLED_bm)

}

```

本示例的代码可从以下 GitHub 资源库中的 non-inverting-pga 文件夹获取。

## 9.4 以数据形式传输到 MPLAB 数据可视化器

本节将使用 Curiosity Nano 上的 AVR DB 的内部运放之一演示同相 PGA 操作。因此,将为单片机编程应用程序以执行以下操作:

- 将 OPAMP0 配置为同相增益放大器

- 使用片上 DAC 和 TCB0 产生 50 Hz 正弦波, 然后馈入 OPAMP0 的同相输入

- 采用片上 TCB1 和 ADC 对 OPAMP0 的输出进行采样

- 将 ADC 结果和 DAC 采样以数据形式通过 USART 传输到 MPLAB 数据可视化器

该应用程序对硬件没有要求,因为所有上述模块和连接均在 AVR DB 内部。

要启动并运行演示,请按照 6. MPLAB 数据可视化器所述步骤操作。要加载的工作区文件是 *non\_inverting\_PGA.json*,可在 GitHub 资源库中获取。 图 9-5 所示为预期结果示例。

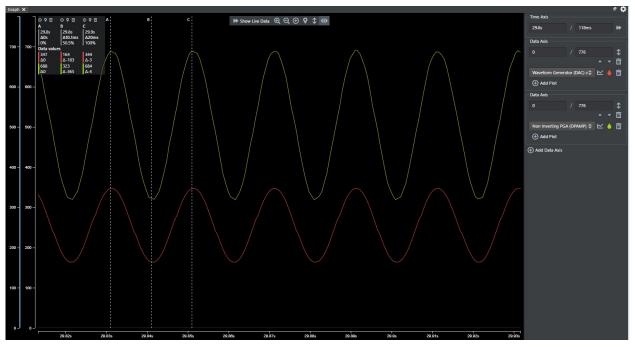

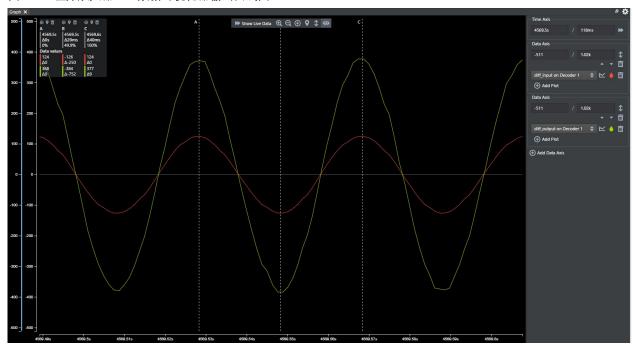

### 图 9-5. 同相 PGA——数据可视化器输出曲线图

在该曲线图中,红色表示 DAC 波形,绿色表示配置为同相 PGA 的 OPAMP0 的采样输出。正如仿真步骤所预期的那样,放大器的输出信号被放大了 2 倍,同时输入信号与输出信号保持同相。

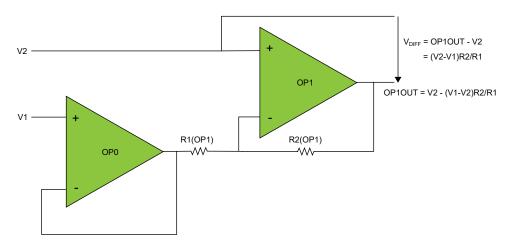

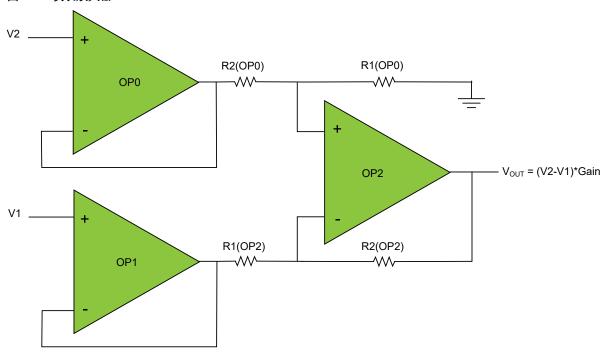

## 10. 差分放大器

图 10-1 所示为由以两个运放连接而成的差分放大器配置。如图所示,差分放大器有两个输入信号 V1 和 V2 以及两个输出信号 OP1OUT 和 V2。两个输出信号之间的差值与两个输入信号之间的差值成比例。两个差分信号之间的比值或增益由 R2 和 R1 之间的比值设置。因此,差分放大器可以放大差分信号。

## 图 10-1. 差分放大器

输出电压 OP1OUT 的计算公式如下:

$$V_{OP1OUT} = V_2 - \left(V_1 - V_2\right)\!\frac{R_2}{R_1}$$

差分信号的计算公式如下:

$$V_{DIFF} = OP1OUT - V_2 = \left(V_2 - V_1\right) \frac{R_2}{R_1}$$

增益为:

$$Gain = \frac{R_2}{R_1}$$

差分放大器适用于提前将较小的差分信号放大,以便随后能够由差分ADC转换为数字信号。

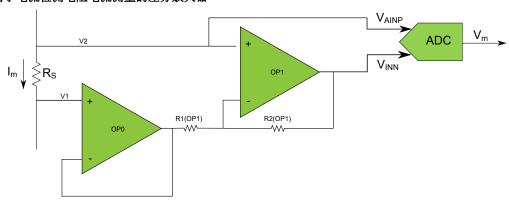

## 10.1 用例

对于带有差分 ADC 的单片机而言,使用电流检测电阻测量电路的电流消耗是一个比较常见的应用。ADC 可测量电阻 两端的压降,随后将测得的电压与已知的电流检测电阻值代入欧姆定律公式即可计算得出电流:

$$I_m = \frac{V_m}{R_S}$$

在电路中引入串联电阻有两个不利影响:

- 增加电路的功耗

- 该电阻两端会出现压降

这两种影响都可以通过选择阻值尽可能低的电阻 R<sub>S</sub> 来得以缓解,这一点对于低功耗应用来说尤为重要。但选择低阻值也有缺点,即测量压降变得更加困难,因为电流变化引起的电压变化非常小。为此,可以使用差分放大器来放大电流检测电阻两端的压降,从而提高测量分辨率。电阻大小对测量分辨率和功耗的影响如表 10-1 所示。

## 表 10-1. 电阻大小与功耗和分辨率的关系

| $R_S[\Omega]$ | 压降[mV] | 功耗[mW] |      | 7x 放大时的分辨率<br>[mA/bit] |

|---------------|--------|--------|------|------------------------|

| 10            | 100    | 1000   | 50   | 7.14                   |

| 1             | 10     | 100    | 500  | 71.4                   |

| 0.1           | 1      | 10     | 5000 | 714                    |

注: 该表假设电流为 10 mA,使用参考电压为 1.024V 的 12 位差分 ADC。

图 10-2 说明了如何在电流检测电阻与 ADC 之间放置一个差分放大器,以便 ADC 能够测量放大的信号。

## 图 10-2. 用于电流检测电阻电流测量的差分放大器

## 10.2 使用 MPLAB Mindi 进行差分放大器模拟仿真

在 MPLAB Mindi 中,打开来自 GitHub 资源库的 Differential\_Amplifier.wxsch 原理图。

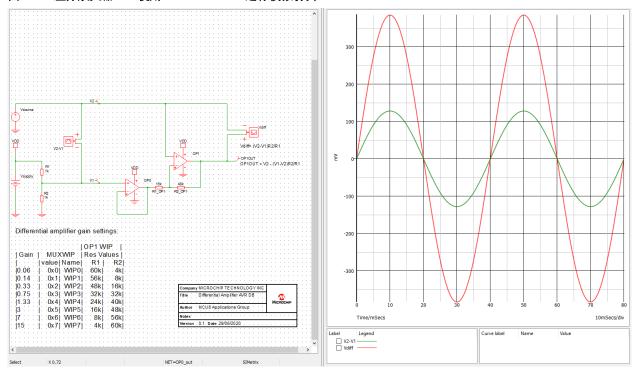

在图 10-3 左半部分所示的电路中,第一个运放由  $V_{DD}/2$  驱动,第二个运放由直流偏移为 1.65V 的 25 Hz 256 m $V_{PP}$  正 弦信号源驱动。这两个运放均由 3.3V 电源供电。

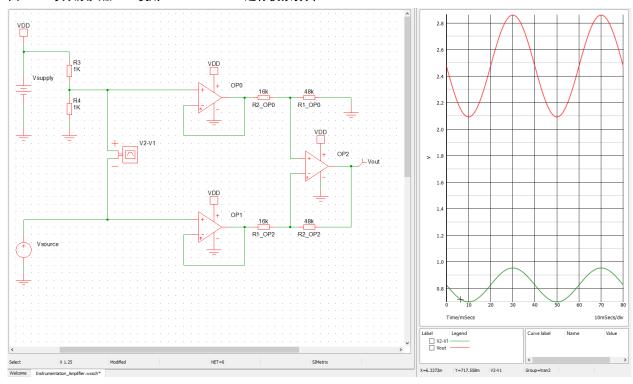

### 图 10-3. 差分放大器——使用 MPLAB Mindi 进行模拟仿真

选择 Simulator  $\rightarrow$  Run Schematic 或按下功能键 F9 进行仿真。最终得到的仿真输出曲线图如图 10-3 的右半部分所示。可以看到,代表差分输出的底部信号的峰值为 $\pm$ 384 mV,符合输入正弦信号相对于  $V_{DD}/2$  的峰值为 $\pm$ 128 mV 的预期。

## 10.3 寄存器配置

上一节简要介绍了差分放大器电路的 MPLAB Mindi 仿真。本节将配置相关 AVR DB OPAMP 寄存器以使能差分放大器配置及操作。有两种选择:

- 运放的同相输入连接到器件的输入引脚

- 运放 n 的同相输入连接到  $V_{DD}/2$ ,运放 n+1 连接到  $DAC^{(1)}$ 。随附的代码示例中使用该配置。

### 表 10-2. 差分放大器的同相输入连接到器件引脚

|                      | MUXPOS | MUXNEG | михвот  | MUXWIP | MUXTOP |

|----------------------|--------|--------|---------|--------|--------|

| OPn                  | INP    | OUT    | OFF     | WIP0   | OFF    |

| OPn+1 <sup>(1)</sup> | INP    | WIP    | LINKOUT | 设置决定增益 | OUT    |

## 表 10-3. 差分放大器的同相输入连接到 VDD/2 和内部 DAC

|                      | MUXPOS  | MUXNEG | михвот | MUXWIP | MUXTOP |

|----------------------|---------|--------|--------|--------|--------|

| OPn                  | VDDDIV2 | OUT    | OFF    | WIP0   | OFF    |

| OPn+1 <sup>(1)</sup> | DAC     | WIP    | LINOUT | 设置决定增益 | OUT    |

## 注:

1. 如果 n = 2,则 OPn+1 为 OP0。

对于差分放大器, OP0 和 OP1 的梯形电阻网络多路开关寄存器分别将配置为 0x00 和 0xB1。这意味着增益为 3。

### 图 10-4. OPAMP.OPnRESMUX——配置梯形电阻网络多路开关

| Bit    | 7           | 6   | 5   | 4           | 3   | 2   | 1    | 0       |

|--------|-------------|-----|-----|-------------|-----|-----|------|---------|

|        | MUXWIP[2:0] |     |     | MUXBOT[2:0] |     |     | MUXT | OP[1:0] |

| Access | R/W         | R/W | R/W | R/W         | R/W | R/W | R/W  | R/W     |

| Reset  | 0           | 0   | 0   | 0           | 0   | 0   | 0    | 0       |

Bits 7:5 - MUXWIP[2:0] Multiplexer for Wiper

This bit field selects the resistor ladder wiper (potentiometer) position.

| Value | Name | Description       |

|-------|------|-------------------|

| 0x0   | WIP0 | R1 = 15R, R2 = 1R |

| 0x1   | WIP1 | R1 = 14R, R2 = 2R |

| 0x2   | WIP2 | R1 = 12R, R2 = 4R |

| 0x3   | WIP3 | R1 = 8R, R2 = 8R  |

| 0x4   | WIP4 | R1 = 6R, R2 = 10R |

| 0x5   | WIP5 | R1 = 4R, R2 = 12R |

| 0x6   | WIP6 | R1 = 2R, R2 = 14R |

| 0x7   | WIP7 | R1 = 1R, R2 = 15R |

## Bits 4:2 - MUXBOT[2:0] Multiplexer for Bottom

This bit field selects the analog signal connected to the bottom resistor in the resistor ladder.

| Value | Name    | Description                                                    |  |

|-------|---------|----------------------------------------------------------------|--|

| 0x0   | OFF     | Multiplexer off                                                |  |

| 0x1   | INP     | Positive input pin for OPn                                     |  |

| 0x2   | INN     | Negative input pin for OPn                                     |  |

| 0x3   | DAC     | DAC output (DAC and DAC output buffer must be enabled)         |  |

| 0x4   | LINKOUT | OP[n-1] output (Setting only available for OP1) <sup>(1)</sup> |  |

| 0x5   | GND     | Ground                                                         |  |

| Other | -       | Reserved                                                       |  |

Note: When selecting LINKOUT for OP0, MUXBOT is connected to the output of OP2.

### Bits 1:0 - MUXTOP[1:0] Multiplexer for Top

This bit field selects the analog signal connected to the top resistor in the resistor ladder.

| Value | Name | Description     |

|-------|------|-----------------|

| 0x0   | OFF  | Multiplexer off |

| 0x1   | OUT  | OPn output      |

| 0x2   | VDD  | $V_{DD}$        |

| Other | -    | Reserved        |

```

OPAMP.OPORESMUX = OPAMP_OPORESMUX_MUXBOT_OFF_gc | OPAMP_OPORESMUX_MUXWIP_WIPO_gc |

OPAMP_OPORESMUX_MUXTOP_OFF_gc;

OPAMP.OP1RESMUX = OPAMP_OP1RESMUX_MUXBOT_LINKOUT_gc | OPAMP_OP1RESMUX_MUXWIP_WIP5_gc |

OPAMP_OP1RESMUX_MUXTOP_OUT_gc;

```

在本文档随附的差分放大器代码示例中,OPO的同相输入连接到 V<sub>DD</sub>/2,OP1 连接到 DAC。

### 图 10-5. OPAMP.OPnINMUX——配置输入多路开关

### Bits 6:4 - MUXNEG[2:0] Multiplexer for Negative Input

This bit field selects which analog signal is connected to the inverting (-) input of OPn.

| Value | Name | Description                                            |

|-------|------|--------------------------------------------------------|

| 0x0   | INN  | Negative input pin for OPn                             |

| 0x1   | WIP  | Wiper from OPn's resistor ladder                       |

| 0x2   | OUT  | OPn output (unity gain)                                |

| 0x3   | DAC  | DAC output (DAC and DAC output buffer must be enabled) |

| Other | -    | Reserved                                               |

#### Bits 2:0 - MUXPOS[2:0] Multiplexer for Positive Input

This bit field selects which analog signal is connected to the non-inverting (+) input of OPn.

| Value | Name    | Description                                                       |

|-------|---------|-------------------------------------------------------------------|

| 0x0   | INP     | Positive input pin for OPn                                        |

| 0x1   | WIP     | Wiper from OPn's resistor ladder                                  |

| 0x2   | DAC     | DAC output (DAC and DAC output buffer must be enabled)            |

| 0x3   | GND     | Ground                                                            |

| 0x4   | VDDDIV2 | $V_{DD/2}$                                                        |

| 0x5   | LINKOUT | OP[n-1] output (Setting only available for OP1 and OP2)           |

| 0x6   | LINKWIP | Wiper from OP0's resistor ladder (Setting only available for OP2) |

| Other | -       | Reserved                                                          |

```

OPAMP.OPOINMUX = OPAMP_OPOINMUX_MUXNEG_OUT_gc | OPAMP_OPOINMUX_MUXPOS_VDDDIV2_gc;

OPAMP.OP1INMUX = OPAMP_OP1INMUX_MUXNEG_WIP_gc | OPAMP_OP1INMUX_MUXPOS_DAC_gc;

```

电压跟随器初始化代码如下所示:

```

void OPAMP init ()

OPAMP.TIMEBASE = OPAMP TIMEBASE US;

/*配置电压输入范围*/

OPAMP.PWRCTRL = OPAMP_PWRCTRL_IRSEL_FULL_gc;

/*配置 OP0 */

OPAMP.OPOCTRLA = OPAMP_OPOCTRLA_OUTMODE_NORMAL_gc | OPAMP_ALWAYSON_bm;

OPAMP.OPOINMUX = OPAMP_OPOINMUX_MUXNEG_OUT_gc | OPAMP_OPOINMUX_MUXPOS_VDDDIV2_gc;

OPAMP.OPORESMUX = OPAMP_OPORESMUX_MUXBOT_OFF_gc | OPAMP_OPORESMUX_MUXWIP_WIPO_gc |

OPAMP OPORESMUX MUXTOP OFF qc;

\overline{OPAMP.OPOSETTLE} = \overline{0} \times 7F;

/*配置 OP1*/

OPAMP.OPICTRLA = OPAMP_OPICTRLA_OUTMODE_NORMAL_gc | OPAMP_ALWAYSON_bm;

OPAMP.OPIINMUX = OPAMP_OPIINMUX_MUXNEG_WIP_gc | OPAMP_OPIINMUX_MUXPOS_DAC_gc;

OPAMP.OP1RESMUX = OPAMP_OP1RESMUX_MUXBOT_LINKOUT_gc | OPAMP_OP1RESMUX_MUXWIP_WIP5_gc |

OPAMP OPIRESMUX MUXTOP OUT gc;

\overline{OPAMP.OP1SETTLE} = \overline{0} \times 7F

/*使能 OPAMP 外设*/

OPAMP.CTRLA = OPAMP_ENABLE_bm;

/*等待运算放大器稳定*/

while ((OPAMP.OPOSTATUS & OPAMP_SETTLED_bm) & (OPAMP.OP1STATUS & OPAMP_SETTLED_bm))

}

```

本示例的代码可从以下 GitHub 资源库中的 differential-amplifier 文件夹获取。

### 10.4 以数据形式传输到 MPLAB 数据可视化器

本节将使用 Curiosity Nano 上的 AVR DB 的两个内部运放演示差分放大器操作。因此,将为单片机编程应用程序以执行以下操作:

- 配置 OPAMP0 和 OPAMP1,以构建差分放大器配置

- OPAMP0 的同相输入连接到 V<sub>DD</sub>/2

- 使用片上 DAC 和 TCB0 产生 25 Hz 正弦波, 然后馈入 OPAMP1 的同相输入

- 采用片上 TCB1 和 ADC 对 DAC 与 OPAMP1 输出之间的差分信号进行采样

- 将 ADC 结果和 DAC 采样(相对于 V<sub>DD</sub>/2)以数据形式通过 USART 传输到 MPLAB 数据可视化器

该应用程序对硬件没有要求,因为所有上述模块和连接均在 AVR DB 内部。

要启动并运行演示,请按照 6. MPLAB 数据可视化器所述步骤操作。要加载的工作区文件是 differential\_amplifier.json,可在 GitHub 资源库中获取。 图 10-6 所示为预期结果示例。

#### 图 10-6. 差分放大器——数据可视化器输出曲线图

在图 10-6 所示的曲线图中,红色表示相对于 V<sub>DD</sub>/2 的 DAC 波形,绿色表示相对于 DAC 输出的 OPAMP1 采样输出。正如仿真步骤所预期的那样,绿色波形的幅值大约是输入波形的 3 倍。至于为何不是准确的 3 倍,主要是由与 DAC、ADC 和 OPAMP 相关的累积误差所致(此类讨论超出本文档的范围)。

# 11. 仪表放大器

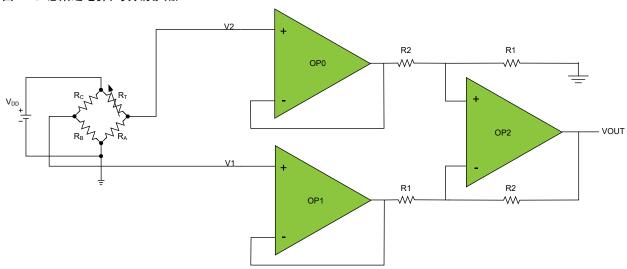

图 11-1 所示为仪表放大器配置。其中有两个输入信号 V1 和 V2 以及一个输出信号 V<sub>OUT</sub>。输出信号与两个输入信号之间的差值成正比。OP0 和 OP1 运放充当 V2-V1 差分输入电压的缓冲器,而 OP2 充当差分放大器(反相和同相放大器的组合)。增益由输出信号与差分输入信号之间的比值表示,通过 R2 与 R1 之间的比值计算。

图 11-1. 仪表放大器

输出电压 VouT 的计算公式如下:

$$V_{OUT} = (V_2 - V_1) \times Gain$$

增益由 OPAMP0 和 OPAMP2 的梯形电阻网络的抽头位置共同决定,如表 11-1 所示。

表 11-1. 仪表放大器的增益选择

| 增益   | OP0RESMUX.MUXWIP | OP2RESMUX.MUXWIP |

|------|------------------|------------------|

| 1/15 | 0x7              | 0x0              |

| 1/7  | 0x6              | 0x1              |

| 1/3  | 0x5              | 0x2              |

| 1    | 0x3              | 0x3              |

| 3    | 0x2              | 0x5              |

| 7    | 0x1              | 0x6              |

| 15   | 0x0              | 0x7              |

通过观察可知,三运放仪表放大器将差分信号作为输入并提供单端输出信号,同时确保将高输入阻抗转换为低输出阻抗。因此,它可以作为差分输出传感器与 ADC 之间的信号调理元件,以便 ADC 能够进行进一步的处理和制定决策。

### 11.1 用例

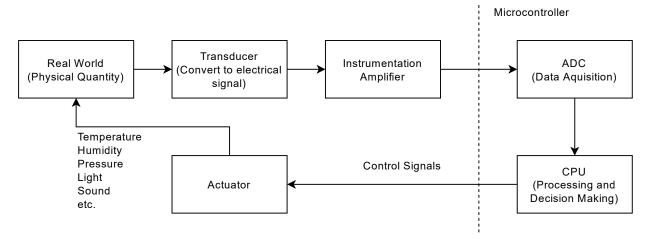

许多电子应用需要测量和控制物理量,例如温度、湿度、光线和气压等。这些物理量会在传感器的作用下转换成电气量。传感器的输出是代表被测变量的电信号。通常,传感器的输出信号非常小,在数据采集过程中对其进行采样之前需要先放大。电信号会被进一步处理和监视,以便根据其变化提供适当的操作。有关简单测量和控制系统的一般框图,请参见图 11-2。用于放大与物理量相关的电信号的放大器通常属于仪表放大器。因此,仪表放大器的输入就是传感器的输出信号。

#### 图 11-2. 测量和控制系统信号流框图

传感器可按多种方式进行分类。但有一点比较重要,即是否需要电源才能正常工作。有源传感器不需要外部电源即可正常工作。这类传感器会自行产生输出信号并遵循能量转换原理(即光伏、热电、电磁和压电等)工作。而无源传感器需要外部电源才能正常工作。这类传感器以电气参数(例如电阻、电容或电感)变化的形式产生输出信号。

惠斯通电桥(或电阻电桥)电路可用于将各种阻性无源传感器连接到仪表放大器(图 11-3)。

#### 图 11-3. 惠斯通电桥和仪表放大器

在该电路中, $R_A$ 、 $R_B$  和  $R_C$  是已知给定的。 $R_T$  代表传感器的电阻,根据随时间变化的物理量而变化。各电阻的值均针对某一特定点来选取,旨在使电桥达到平衡状态。

当达到平衡状态时,  $\frac{R_C}{R_B} = \frac{R_T}{R_A} = 1$ , 惠斯通电桥的输出电压(以及仪表放大器的差分输入)为零,因此放大器的输出为零。

当被测物理量发生变化时,电压 V2 将不再等于 V1。传感器器件的电阻从  $R_T$  变为  $R_T \pm \Delta R$ 。这将为仪表放大器产生差分电压输入,放大器的输出将不再为零。

$$V_1 = \frac{R_B}{R_B + R_C} \times V_{DD}$$

$$V_2 = \frac{R_A}{R_A + R_T \pm \Delta R} \times V_{DD}$$

假设为所有电阻选择相同的值,即: $R_A = R_B = R_C = R_T = R$ ,则差分电压输入将变为:

$$V_2 - V_1 = \frac{R}{2R} \times V_{DD} - \frac{R}{2R \pm \Delta R} \times V_{DD}$$

$$V_2 - V_1 = \frac{\pm \Delta R}{2(2R \pm \Delta R)} \times V_{DD}$$

如果电阻的变化  $\Delta R$  远小于 2R ( $\Delta R << 2R$ ),则公式可简化为:

$$V_2 - V_1 = \frac{\pm \Delta R}{4R} \times V_{DD}$$

因此, 仪表放大器的输出可表示为:

$$V_{OUT} = Gain \times \frac{\pm \Delta R}{4R} \times V_{DD}$$

这意味着仪表放大器的输出电压直接取决于:

- 传感器电阻的变化 ΔR

- 放大器的增益(见表 11-1):

需要特别注意的是,差分电压  $V_2$ - $V_1$  必须始终为正。这是负轨的 0V 运放电源轨电压与正轨的+ $V_{DD}$  共同作用的结果。因此,在惠斯通电桥配置中放置传感器时必须小心谨慎。传感器位置取决于激励时电阻的正/负变化。

惠斯通电桥和仪表放大器可用于多种传感应用,例如:

- 基于热敏电阻的温度传感器

- 基于力敏电阻(Force-Sensitive Resistor, FSR)的力传感器

- 基于应变计的体重秤

### 11.2 使用 MPLAB Mindi 进行仪表放大器模拟仿真

在 MPLAB Mindi 中,打开来自 GitHub 资源库的 Instrumentation Amplifier.wxsch 原理图。

图 11-4 左半部分所示电路由具有 825 mV 直流失调的 25 Hz、256 mV<sub>PP</sub> 正弦差分信号源驱动。运放由 3.3V 电压源供电。

#### 图 11-4. 仪表放大器——使用 MPLAB Mindi 进行模拟仿真

选择 Simulator → Run Schematic 或按下功能键 F9 进行仿真。最终得到的仿真输出曲线图如图 11-4 的右半部分所示。我们注意到,输出信号(红色)是输入信号(绿色)的三倍且保持同相。

### 11.3 寄存器配置

上一节简要介绍了仪表放大器电路的 MPLAB Mindi 仿真。本节将配置相关 AVR DB OPAMP 外设寄存器以使能仪表放大器拓扑及操作,具体如下:

- OP0 运放设置为电压跟随器,同相输入在内部连接到 V<sub>DD/2</sub>。梯形电阻网络的顶部连接到运放的输出,底部接地,抽头位置根据表 11-1 选择。

- OP1 运放设置为电压跟随器,同相输入在内部连接到板上 DAC。不使用梯形电阻网络。

- OP2 运放设置为将来自 OP0 梯形电阻网络的抽头连接作为同相输入,将 OP2 梯形电阻网络的抽头位置作为反相输入。梯形电阻网络的顶部连接到运放的输出,底部连接到 OP1 运放,抽头位置根据表 11-1 选择。

表 11-2 总结了将三个内部运放设置为仪表放大器配置所需的设置。

表 11-2. 仪表放大器连接到内部 DAC

|     | MUXPOS              | MUXNEG | михвот              | MUXWIP | MUXTOP |

|-----|---------------------|--------|---------------------|--------|--------|

| OP0 | V <sub>DD/2</sub>   | OUT    | GND                 | 见下表    | OUT    |

| OP1 | DAC                 | OUT    | OFF                 | WIP0   | OFF    |

| OP2 | LINKWIP<br>(OP0WIP) | WIP    | LINKOUT<br>(OP1OUT) | 见下表    | OUT    |

对于仪表放大器,每个放大器的梯形电阻网络多路开关寄存器将单独配置。

#### 图 11-5. OPAMP.OPnRESMUX——配置梯形电阻网络多路开关

| Bit    | 7   | 6           | 5   | 4   | 3           | 2   | 1    | 0       |

|--------|-----|-------------|-----|-----|-------------|-----|------|---------|

|        |     | MUXWIP[2:0] |     |     | MUXBOT[2:0] |     | MUXT | OP[1:0] |

| Access | R/W | R/W         | R/W | R/W | R/W         | R/W | R/W  | R/W     |

| Reset  | 0   | 0           | 0   | 0   | 0           | 0   | 0    | 0       |

#### Bits 7:5 - MUXWIP[2:0] Multiplexer for Wiper

This bit field selects the resistor ladder wiper (potentiometer) position.

| Value | Name | Description       |

|-------|------|-------------------|

| 0x0   | WIP0 | R1 = 15R, R2 = 1R |

| 0x1   | WIP1 | R1 = 14R, R2 = 2R |

| 0x2   | WIP2 | R1 = 12R, R2 = 4R |

| 0x3   | WIP3 | R1 = 8R, R2 = 8R  |

| 0x4   | WIP4 | R1 = 6R, R2 = 10R |

| 0x5   | WIP5 | R1 = 4R, R2 = 12R |

| 0x6   | WIP6 | R1 = 2R, R2 = 14R |

| 0x7   | WIP7 | R1 = 1R, R2 = 15R |

#### Bits 4:2 - MUXBOT[2:0] Multiplexer for Bottom

This bit field selects the analog signal connected to the bottom resistor in the resistor ladder.

| Value | Name    | Description                                                    |

|-------|---------|----------------------------------------------------------------|

| 0x0   | OFF     | Multiplexer off                                                |

| 0x1   | INP     | Positive input pin for OPn                                     |

| 0x2   | INN     | Negative input pin for OPn                                     |

| 0x3   | DAC     | DAC output (DAC and DAC output buffer must be enabled)         |

| 0×4   | LINKOUT | OP[n-1] output (Setting only available for OP1) <sup>(1)</sup> |

| 0x5   | GND     | Ground                                                         |

| Other | -       | Reserved                                                       |

Note: When selecting LINKOUT for OP0, MUXBOT is connected to the output of OP2.

#### Bits 1:0 - MUXTOP[1:0] Multiplexer for Top

This bit field selects the analog signal connected to the top resistor in the resistor ladder.

| Value | Name | Description     |

|-------|------|-----------------|

| 0x0   | OFF  | Multiplexer off |

| 0x1   | OUT  | OPn output      |

| 0x2   | VDD  | $V_{DD}$        |

| Other | -    | Reserved        |

```

OPAMP.OPORESMUX = OPAMP_OPORESMUX_MUXBOT_GND_gc | OPAMP_OPORESMUX_MUXWIP_WIP2_gc |

OPAMP_OPORESMUX_MUXTOP_OUT_gc;

OPAMP.OP1RESMUX = OPAMP_OP1RESMUX_MUXBOT_OFF_gc | OPAMP_OP1RESMUX_MUXWIP_WIP0_gc |

OPAMP_OP1RESMUX_MUXTOP_OFF_gc;

OPAMP.OP2RESMUX = OPAMP_OP2RESMUX_MUXBOT_LINKOUT_gc | OPAMP_OP2RESMUX_MUXWIP_WIP5_gc |

OPAMP_OP2RESMUX_MUXTOP_OUT_gc;

```

每个放大器的同相输入和反相输入也是如此。它们需要按照表 11-2 所示单独配置。

#### 图 11-6. OPAMP.OPnINMUX——配置输入多路开关

#### Bits 6:4 - MUXNEG[2:0] Multiplexer for Negative Input

This bit field selects which analog signal is connected to the inverting (-) input of OPn.

| Value | Name | Description                                            |

|-------|------|--------------------------------------------------------|

| 0x0   | INN  | Negative input pin for OPn                             |

| 0x1   | WIP  | Wiper from OPn's resistor ladder                       |

| 0x2   | OUT  | OPn output (unity gain)                                |

| 0x3   | DAC  | DAC output (DAC and DAC output buffer must be enabled) |

| Other | -    | Reserved                                               |

#### Bits 2:0 - MUXPOS[2:0] Multiplexer for Positive Input

This bit field selects which analog signal is connected to the non-inverting (+) input of OPn.

| Value | Name    | Description                                                       |

|-------|---------|-------------------------------------------------------------------|

| 0x0   | INP     | Positive input pin for OPn                                        |

| 0x1   | WIP     | Wiper from OPn's resistor ladder                                  |

| 0x2   | DAC     | DAC output (DAC and DAC output buffer must be enabled)            |

| 0x3   | GND     | Ground                                                            |

| 0x4   | VDDDIV2 | $V_{DD/2}$                                                        |

| 0x5   | LINKOUT | OP[n-1] output (Setting only available for OP1 and OP2)           |

| 0x6   | LINKWIP | Wiper from OP0's resistor ladder (Setting only available for OP2) |

| Other | -       | Reserved                                                          |

```

OPAMP.OPOINMUX = OPAMP OPOINMUX MUXNEG OUT gc | OPAMP OPOINMUX MUXPOS VDDDIV2 gc;

OPAMP.OP1INMUX = OPAMP OP1INMUX MUXNEG OUT gc | OPAMP OP1INMUX MUXPOS DAC gc;

OPAMP.OP2INMUX = OPAMP OP2INMUX MUXNEG WIP gc | OPAMP OP2INMUX MUXPOS LINKWIP gc;

```

#### 仪表放大器初始化代码如下所示:

```

void OPAMP_init (void)

/*配置时基*/

OPAMP.TIMEBASE = OPAMP_TIMEBASE_US;

/*配置电压输入范围*/

OPAMP.PWRCTRL = OPAMP_PWRCTRL_IRSEL_FULL_gc;

OPAMP.OPOCTRLA = OPAMP_OPOCTRLA_OUTMODE_NORMAL_gc | OPAMP_ALWAYSON_bm;

OPAMP.OPOINMUX = OPAMPOPOINMUX_MUXNEG_OUT_gc | OPAMP_OPOINMUX MUXPOS VDDDIV2 gc;

OPAMP.OPORESMUX = OPAMP OPORESMUX MUXBOT GND gc | OPAMP OPORESMUX MUXWIP WIP2 gc |

OPAMP OPORESMUX MUXTOP OUT gc;

OPAMP.OPOSETTLE = 0 \times 7F;

/*配置 OP1*/

OPAMP.OPICTRLA = OPAMP_OPICTRLA_OUTMODE_NORMAL_gc | OPAMP_ALWAYSON_bm;

OPAMP.OP1INMUX = OPAMP_OP1INMUX_MUXNEG_OUT_gc | OPAMP_OP1INMUX_MUXPOS_DAC_gc;

OPAMP.OPIRESMUX = OPAMP OPIRESMUX MUXBOT OFF gc | OPAMP OPIRESMUX MUXWIP WIPO gc |

OPAMP OP1RESMUX_MUXTOP_OFF_gc;

\overline{OPAMP.OP1SETTLE} = \overline{0}x7F;

/*配置 OP2*/

OPAMP.OP2CTRLA = OPAMP_OP2CTRLA_OUTMODE_NORMAL_gc | OPAMP_ALWAYSON_bm;

OPAMP.OP2INMUX = OPAMP_OP2INMUX_MUXNEG_WIP_gc; OPAMP_OP2INMUX_MUXPOS_LINKWIP_gc;

OPAMP.OP2RESMUX = OPAMP OP2RESMUX MUXBOT LINKOUT gc | OPAMP OP2RESMUX MUXWIP WIP5 gc |

OPAMP OP2RESMUX_MUXTOP_OUT_gc;

\overline{OPAMP.OP2SETTLE} = \overline{0x7F}

/*使能 OPAMP 外设*/

OPAMP.CTRLA = OPAMP_ENABLE_bm;

/*等待运算放大器稳定*/

```

本示例的代码可从以下 GitHub 资源库中的 instrumentation-amplifier 文件夹获取。

### 11.4 以数据形式传输到 MPLAB 数据可视化器

本节将使用 Curiosity Nano 上的 AVR DB 的全部三个内部运放演示仪表放大器操作。因此,将为单片机编程应用程序以执行以下操作:

- 将 OPAMP0 配置为电压跟随器,同相端子的输入为 V<sub>DD</sub>/2

- 使用片上 DAC 和 TCB0 产生 25 Hz 正弦波,然后馈入配置为电压跟随器的 OPAMP1 的同相输入

- 将 OPAMP2 设置为差分放大器,其中输入为 OPAMP0 和 OPAMP1 电压跟随器的输出

- 采用片上 TCB1 和 ADC 对 OPAMP2 的输出进行采样

- 将 ADC 结果和 DAC 采样以数据形式通过 USART 传输到 MPLAB 数据可视化器

该应用程序对硬件没有要求,因为所有上述模块和连接均在 AVR DB 内部。

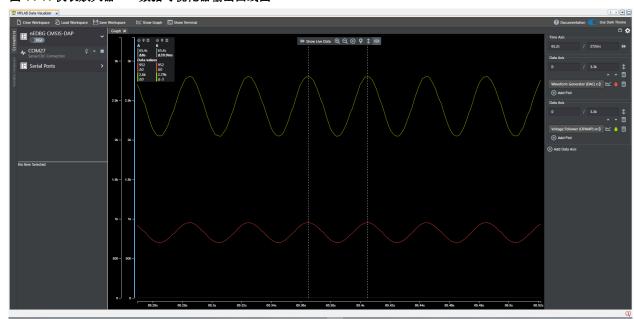

要启动并运行演示,请按照 6. MPLAB 数据可视化器所述步骤操作。要加载的工作区文件是 *instrumentation\_amplifier.json*,可在 GitHub 资源库中获取。 图 11-7 所示为预期结果示例。

#### 图 11-7. 仪表放大器——数据可视化器输出曲线图

在该曲线图中,红色表示 DAC 波形,石灰绿表示 OPAMP2 的采样输出(与仪表放大器的输出相同)。正如仿真步骤 所预期的那样,放大器的输出信号被放大了 3 倍,同时输入信号与输出信号保持同相。

# 12. 参考资料

有关模拟信号调理模块及演示其工作模式所使用的工具的更多信息,请访问以下链接:

- 1. AVR DB 产品页面: www.microchip.com/wwwproducts/en/AVR128DB48

- 2. AVR DB Curiosity Nano: www.microchip.com/DevelopmentTools/ProductDetails/PartNO/EV35L43A

- 3. MPLAB Mindi 模拟仿真器产品页面: www.microchip.com/mplab/mplab-mindi

- 4. MPLAB Mindi 模拟仿真器入门: www.microchip.com/DS50002564

- 5. MPLAB 数据可视化器 Standalone(Windows 版): gallery.microchip.com/packages/MPLAB-Data-Visualizer-Standalone(Windows)/

- 6. MPLAB 数据可视化器软件用户指南: www.microchip.com/DS50003001

# 13. 版本历史

| 文档版本 | 日期      | 备注     |

|------|---------|--------|

| Α    | 2020年9月 | 文档初始版本 |

# Microchip 网站

**Microchip** 网站(www.microchip.com/)为客户提供在线支持。客户可通过该网站方便地获取文件和信息。我们的网站提供以下内容:

- **产品支持**——数据手册和勘误表、应用笔记和示例程序、设计资源、用户指南以及硬件支持文档、最新的软件版本以及归档软件

- 一般技术支持——常见问题解答(FAQ)、技术支持请求、在线讨论组以及 Microchip 设计伙伴计划成员名单

- **Microchip 业务**——产品选型和订购指南、最新 **Microchip** 新闻稿、研讨会和活动安排表、**Microchip** 销售办事 处、代理商以及工厂代表列表

## 产品变更通知服务

Microchip 的产品变更通知服务有助于客户了解 Microchip 产品的最新信息。注册客户可在他们感兴趣的某个产品系列或开发工具发生变更、更新、发布新版本或勘误表时,收到电子邮件通知。

欲注册,请访问 www.microchip.com/pcn,然后按照注册说明进行操作。

## 客户支持

Microchip 产品的用户可通过以下渠道获得帮助:

- 代理商或代表

- 当地销售办事处

- 应用工程师(ESE)

- 技术支持

客户应联系其代理商、代表或 ESE 寻求支持。当地销售办事处也可为客户提供帮助。本文档后附有销售办事处的联系方式。

也可通过 www.microchip.com/support 获得网上技术支持。

# Microchip 器件代码保护功能

请注意以下有关 Microchip 产品代码保护功能的要点:

- Microchip 的产品均达到 Microchip 数据手册中所述的技术规范。

- Microchip 确信:在正常使用且符合工作规范的情况下, Microchip 系列产品非常安全。

- Microchip 注重并积极保护其知识产权。严禁任何试图破坏 Microchip 产品代码保护功能的行为,这种行为可能会 违反《数字千年版权法案》(Digital Millennium Copyright Act)。

- Microchip 或任何其他半导体厂商均无法保证其代码的安全性。代码保护并不意味着我们保证产品是"牢不可破"的。代码保护功能处于持续发展中。Microchip 承诺将不断改进产品的代码保护功能。

# 法律声明

提供本文档的中文版本仅为了便于理解。请勿忽视文档中包含的英文部分,因为其中提供了有关 Microchip 产品性能和使用情况的有用信息。Microchip Technology Inc.及其分公司和相关公司、各级主管与员工及事务代理机构对译文中可能存在的任何差错不承担任何责任。建议参考 Microchip Technology Inc.的英文原版文档。

本出版物及其提供的信息仅适用于 Microchip 产品,包括设计、测试以及将 Microchip 产品集成到您的应用中。以其他任何方式使用这些信息都将被视为违反条款。本出版物中的器件应用信息仅为您提供便利,将来可能会发生更新。如需额外的支持,请联系当地的 Microchip 销售办事处,或访问 https://www.microchip.com/en-us/support/design-help/client-supportservices。

© 2021 Microchip Technology Inc. 技术简介 DS90003286A\_CN-第 47 页

Microchip"按原样"提供这些信息。Microchip 对这些信息不作任何明示或暗示、书面或口头、法定或其他形式的声明或担保,包括但不限于针对非侵权性、适销性和特定用途的适用性的暗示担保,或针对其使用情况、质量或性能的担保。

在任何情况下,对于因这些信息或使用这些信息而产生的任何间接的、特殊的、惩罚性的、偶然的或间接的损失、损害或任何类型的开销,Microchip 概不承担任何责任,即使 Microchip 已被告知可能发生损害或损害可以预见。在法律允许的最大范围内,对于因这些信息或使用这些信息而产生的所有索赔,Microchip 在任何情况下所承担的全部责任均不超出您为获得这些信息向 Microchip 直接支付的金额(如有)。如果将 Microchip 器件用于生命维持和/或生命安全应用,一切风险由买方自负。买方同意在由此引发任何一切损害、索赔、诉讼或费用时,会维护和保障 Microchip 免于承担法律责任。除非另外声明,在 Microchip 知识产权保护下,不得暗中或以其他方式转让任何许可证。

## 商标

Microchip 的名称和徽标组合、Microchip 徽标、Adaptec、AnyRate、AVR、AVR 徽标、AVR Freaks、BesTime、BitCloud、CryptoMemory、CryptoRF、dsPIC、flexPWR、HELDO、IGLOO、JukeBlox、KeeLoq、Kleer、LANCheck、LinkMD、maXStylus、maXTouch、MediaLB、megaAVR、Microsemi、Microsemi 徽标、MOST、MOST 徽标、MPLAB、OptoLyzer、PIC、picoPower、PICSTART、PIC32 徽标、PolarFire、Prochip Designer、QTouch、SAM-BA、SenGenuity、SpyNIC、SST、SST 徽标、SuperFlash、Symmetricom、SyncServer、Tachyon、TimeSource、tinyAVR、UNI/O、Vectron 及 XMEGA 均为 Microchip Technology Incorporated 在美国和其他国家或地区的注册商标。

AgileSwitch、APT、ClockWorks、The Embedded Control Solutions Company、EtherSynch、Flashtec、Hyper Speed Control、HyperLight Load、IntelliMOS、Libero、motorBench、mTouch、Powermite 3、Precision Edge、ProASIC、ProASIC Plus、ProASIC Plus 徽标、Quiet-Wire、SmartFusion、SyncWorld、Temux、TimeCesium、TimeHub、TimePictra、TimeProvider、TrueTime、WinPath 和 ZL 均为 Microchip Technology Incorporated 在美国的注册商标。

Adjacent Key Suppression、AKS、Analog-for-the-Digital Age、Any Capacitor、Anyln、AnyOut、Augmented Switching、BlueSky、BodyCom、CodeGuard、CryptoAuthentication、CryptoAutomotive、CryptoCompanion、CryptoController、dsPICDEM、dsPICDEM.net、Dynamic Average Matching、DAM、ECAN、Espresso T1S、EtherGREEN、GridTime、IdealBridge、In-Circuit Serial Programming、ICSP、INICnet、Intelligent Paralleling、Inter-Chip Connectivity、JitterBlocker、Knob-on-Display、maxCrypto、maxView、memBrain、Mindi、MiWi、MPASM、MPF、MPLAB Certified 徽标、MPLIB、MPLINK、MultiTRAK、NetDetach、NVM Express、NVMe、Omniscient Code Generation、PICDEM、PICDEM.net、PICkit、PICtail、PowerSmart、PureSilicon、QMatrix、REAL ICE、Ripple Blocker、RTAX、RTG4、SAM-ICE、Serial Quad I/O、simpleMAP、SimpliPHY、SmartBuffer、SmartHLS、SMART-I.S.、storClad、SQI、SuperSwitcher、SuperSwitcher II、Switchtec、SynchroPHY、Total Endurance、TSHARC、USBCheck、VariSense、VectorBlox、VeriPHY、ViewSpan、WiperLock、XpressConnect 和 ZENA 均为 Microchip Technology Incorporated 在美国和其他国家或地区的商标。

SQTP 为 Microchip Technology Incorporated 在美国的服务标记。

Adaptec 徽标、Frequency on Demand、Silicon Storage Technology、Symmcom 和 Trusted Time 均为 Microchip Technology Inc.在除美国外的国家或地区的注册商标。

GestIC 为 Microchip Technology Inc.的子公司 Microchip Technology Germany II GmbH & Co. KG 在除美国外的国家或地区的注册商标。

在此提及的所有其他商标均为各持有公司所有。

© 2021, Microchip Technology Incorporated 及其子公司版权所有。

ISBN: 978-1-5224-8822-4

# 质量管理体系

有关 Microchip 的质量管理体系的信息,请访问 www.microchip.com/quality。

# 全球销售及服务网点

| 美洲                                              | 亚太地区                                  | 亚太地区                | 欧洲                   |

|-------------------------------------------------|---------------------------------------|---------------------|----------------------|

|                                                 | 澳大利亚 - 悉尼                             | 印度 - 班加罗尔           | 奥地利 - 韦尔斯            |

| 355 West Chandler Blvd.                         | 电话: 61-2-9868-6733                    | 电话: 91-80-3090-4444 | 电话: 43-7242-2244-39  |

| Chandler, AZ 85224-6199                         | 中国 - 北京                               | 印度 - 新德里            | 传真: 43-7242-2244-393 |

| 电话: 480-792-7200                                | 电话: 86-10-8569-7000                   | 电话: 91-11-4160-8631 | 丹麦 - 哥本哈根            |

| 专真: 480-792-7277                                | 中国 - 成都                               | 印度 - 浦那             | 电话: 45-4485-5910     |

| 支术支持:                                           | 电话: 86-28-8665-5511                   | 电话: 91-20-4121-0141 | 传真: 45-4485-2829     |

| vww.microchip.com/support                       | 中国 - 重庆                               | 日本 - 大阪             | 芬兰 - 埃斯波             |

| 网址:                                             | 电话: 86-23-8980-9588                   | 电话: 81-6-6152-7160  | 电话: 358-9-4520-820   |

| www.microchip.com                               | 中国 - 东莞                               | 日本 - 东京             | 法国 - 巴黎              |

| ☑特兰大                                            | ' ' ' ' ' ' ' '                       | 电话: 81-3-6880-3770  |                      |

| <b>恵に上</b> り、<br>恵卢斯,佐治亚州                       | 电话: 86-769-8702-9880                  |                     | 电话: 33-1-69-53-63-20 |

| 电话: 678-957-9614                                | 中国 - 广州                               | 韩国 - 大邱             | 传真: 33-1-69-30-90-79 |

| 专真:678-957-1455                                 | 电话: 86-20-8755-8029                   | 电话: 82-53-744-4301  | 德国 - 加兴              |

| <sup>支兵: 070-937-1433</sup><br><b>奥斯汀,德克萨斯州</b> | 中国 - 杭州                               | 韩国 - 首尔             | 电话: 49-8931-9700     |

|                                                 | 电话: 86-571-8792-8115                  | 电话: 82-2-554-7200   | 德国 - 哈恩              |

| 电话: 512-257-3370                                | 中国 - 香港特别行政区                          | 马来西亚 - 吉隆坡          | 电话: 49-2129-3766400  |

| <b>皮士顿</b><br>卡斯快角鱼 丑恭老寒叫                       | 电话: 852-2943-5100                     | 电话: 60-3-7651-7906  | 德国 - 海尔布隆            |

| 事事特伯鲁,马萨诸塞州<br>□ 374 700 0007                   | 中国 - 南京                               | 马来西亚 - 槟榔屿          | 电话: 49-7131-72400    |

| 电话: 774-760-0087                                | 电话: 86-25-8473-2460                   | 电话: 60-4-227-8870   | 德国 - 卡尔斯鲁厄           |

| 专真: 774-760-0088                                | 中国 - 青岛                               | 菲律宾 - 马尼拉           | 电话: 49-721-625370    |

| <b>芝加哥</b>                                      | 电话: 86-532-8502-7355                  | 电话: 63-2-634-9065   | 德国 - 慕尼黑             |

| 艾塔斯卡,伊利诺伊州                                      | 中国 - 上海                               | 新加坡                 | 电话: 49-89-627-144-0  |

| <b>电话:630-285-0071</b>                          | 电话: 86-21-3326-8000                   | 电话: 65-6334-8870    | 传真: 49-89-627-144-44 |

| 专真: 630-285-0075                                | 中国 - 沈阳                               | 台湾地区 - 新竹           | 德国 - 罗森海姆            |

| <b>达拉斯</b>                                      | 电话: 86-24-2334-2829                   | 电话: 886-3-577-8366  | 电话: 49-8031-354-560  |

| 可迪森,德克萨斯州                                       | 中国 - 深圳                               | 台湾地区 - 高雄           | 以色列 - 若那那市           |

| 电话: 972-818-7423                                | 电话: 86-755-8864-2200                  | 电话: 886-7-213-7830  | 电话: 972-9-744-7705   |

| 专真: 972-818-2924                                | 中国 - 苏州                               | 台湾地区 - 台北           | 意大利 - 米兰             |

| <b>装特律</b>                                      | 电话: 86-186-6233-1526                  | 电话: 886-2-2508-8600 | 电话: 39-0331-742611   |

| 若维, 密歇根州                                        | 中国 - 武汉                               | 泰国 - 曼谷             | 传真: 39-0331-466781   |

| 电话: 248-848-4000                                | · · · · · · · · · · · · · · · · · · · | 电话: 66-2-694-1351   | 意大利 - 帕多瓦            |

| 木斯顿,德克萨斯州                                       | 电话: 86-27-5980-5300                   |                     |                      |

| 电话: 281-894-5983                                | 中国 - 西安                               | 越南 - 胡志明市           | 电话: 39-049-7625286   |

| 印第安纳波利斯                                         | 电话: 86-29-8833-7252                   | 电话: 84-28-5448-2100 | 荷兰 - 德卢内市            |

| 若布尔斯维尔, 印第安纳州                                   | 中国 - 厦门                               |                     | 电话: 31-416-690399    |

| <b>电话:317-773-8323</b>                          | 电话: 86-592-2388138                    |                     | 传真: 31-416-690340    |

| 专真: 317-773-5453                                | 中国 - 珠海                               |                     | 挪威 - 特隆赫姆            |

| 电话: 317-536-2380                                | 电话: 86-756-3210040                    |                     | 电话: 47-72884388      |

| 8杉矶                                             |                                       |                     | 波兰 - 华沙              |

| <b>ド</b> 慎维荷,加利福尼亚州                             |                                       |                     | 电话: 48-22-3325737    |

| 电话: 949-462-9523                                |                                       |                     | 罗马尼亚 - 布加勒斯特         |

| 专真:949-462-9608                                 |                                       |                     | 电话: 40-21-407-87-50  |

|                                                 |                                       |                     | 西班牙 - 马德里            |

| 电话: 951-273-7800                                |                                       |                     | 电话: 34-91-708-08-90  |

| 罗利,北卡罗来纳州                                       |                                       |                     | 传真: 34-91-708-08-91  |

| <b>电话: 919-844-7510</b>                         |                                       |                     | 瑞典 - 哥德堡             |

| 丑约,纽约州                                          |                                       |                     | 电话: 46-31-704-60-40  |

| 电话: 631-435-6000                                |                                       |                     | 瑞典 - 斯德哥尔摩           |

| <b>圣何塞,加利福尼亚州</b>                               |                                       |                     | 电话: 46-8-5090-4654   |

| 电话: 408-735-9110                                |                                       |                     | I .T.                |

| 电话: 408-436-4270                                |                                       |                     | 英国 - 沃金厄姆            |

| 加拿大 - 多伦多                                       |                                       |                     | 电话: 44-118-921-5800  |

| 旦话: 905-695-1980                                |                                       |                     | 传真: 44-118-921-5820  |

| 专真: 905-695-2078                                |                                       |                     |                      |