STM32H7 以太网的 MMC 中断

关键字: STM32H7, Ethernet

# 前言

STM32H7 以太网的 MMC(MAC management counter)中断是个有点特别的中断。特殊之处在于它是默认使能。如果我们在代码里不针对 MMC 进行相关处理,就会造成一些异常现象。我们先来看一个真实的客户案例。

# 客户案例

客户使用 STM32H750 作为主控,与其他设备之间进行以太网通讯。客户在压力测试中发现:

- 设备从第一次通讯开始,累计 7 到 8 天,就会发现 STM32H750 不再响应用户的请求。

- 客户通过使用 IDE 和添加辅助代码可以发现,STM32H750 会不停地进入以太 网中断,导致所使用的操作系统无法进行有效的系统调度。

- 问题发生后,客户无论拔下网线或者再次连上网线,STM32H750 依然会不停的进入以太网中断。

- 客户尝试使用 IDE 查看所有以太网寄存器,会发现有时侯能够让系统恢复正常。

# 分析

系统不停的进入以太网中断,说明某个中断在被某种条件下被不停的触发,或者中断触发后没有被处理。进一步,当系统出现异常状况后,拔掉网线,中断依然不断的进入,说明该异常并不需要外界不停的输入,也就说明可能是中断没有被处理所导致。所以,客户首先想到的是补全所有使能的以太网中断的清除代码。然而,客户再次测试,却发现累计7到8天,问题再次发生。在这种情况下,为了深刻了解该状况的原因,我们建议客户,抓取异常时的寄存器现场,然后和正常状态时的寄存器进行对比。我们在设备未发生异常前,抓取了以太网的三组寄存器 DMA、MTL 和 MAC。同时,我们在发生异常后,在同一设备再次进行这三组寄存器的抓取。然后,我们使用文本比较工具,对两次的寄存器进行比较。我们很快就可以发现,MAC 寄存器存在值得关注的差异。MAC 寄存器对比如下:

图 1 MAC 寄存器对比

| VLI            | uxuuuu keadwrite     |            | 82  | VLI            | ихииии    | кеадwrite     |

|----------------|----------------------|------------|-----|----------------|-----------|---------------|

| MACQTxFCR      | 0x00000000 ReadWrite |            | 83  | MACQTxFCR      | 0x00000   | 000 ReadWrite |

| PT 0x0000      | ReadWrite            |            | 84  | PT 0x0000      | ReadWrite |               |

| DZPQ           | 0 ReadWrite          |            | 85  | DZPQ           | 0         | ReadWrite     |

| PLT            | 0x0 ReadWrite        |            | 86  | PLT            | 0x0       | ReadWrite     |

| TFE            | 0 ReadWrite          |            | 87  | TFE            | 0         | ReadWrite     |

| FCB_BPA        | 0 ReadWrite          |            | 88  | FCB_BPA        | 0         | ReadWrite     |

| MACRxFCR       | 0x00000000 ReadWrite |            | 89  | MACRxFCR       | 0x00000   | 000 ReadWrite |

| UP Ø           | ReadWrite            |            | 90  | UP Ø           | ReadWrite |               |

| RFE            | 0 ReadWrite          |            | 91  | RFE            | 0         | ReadWrite     |

| MACISR 0x00000 | 00 ReadOnly          | <b>(</b>   | 92  | MACISR 0x00000 | 000       | ReadOnly      |

| RXSTSIS        | 0 ReadOnly           |            | 93  | RXSTSIS        | 0         | ReadOnly      |

| TXSTSIS        | 0 ReadOnly           |            | 94  | TXSTSIS        | 0         | ReadOnly      |

| TSIS           | 0 ReadOnly           |            | 95  | TSIS           | 0         | ReadOnly      |

| MMCTXIS        | 0 ReadOnly           |            | 96  | MMCTXIS        | 0         | ReadOnly      |

| MMCRXIS        | 1 ReadOnly           | <b>(</b> - | 97  | MMCRXIS        | 0         | ReadOnly      |

| MMCIS          | 1 ReadOnly           |            | 98  | MMCIS          | 0         | ReadOnly      |

| LPIIS          | 0 ReadOnly           |            | 99  | LPIIS          | 0         | ReadOnly      |

| PMTIS          | 0 ReadOnly           |            | 100 | PMTIS          | 0         | ReadOnly      |

| PHYIS          | 0 ReadOnly           |            | 101 | PHYIS          | 0         | ReadOnly      |

我们可以看到在系统异常情况下下,MMCRXIS 和 MMCIS 被置位了。

我们从参考手册 RM0433 (STM32H742, STM32H743/753 and STM32H750 Value line advanced Arm®-based 32-bit MCUs) (直接搜索关键子 MMCRXIS) 中可以看到 MMCRXIS 和 MMCIS 表示系统收到了 MMC 接收中断。

#### 图 2 MMCRXIS 与 MMCIS 置位的含义

#### Bit 9 MMCRXIS: MMC Receive Interrupt Status

This bit is set high when an interrupt is generated in the MMC Receive Interrupt Register. This bit is cleared when all bits in this interrupt register are cleared.

This bit is valid only when you select the Enable MAC Management Counters (MMC) option.

#### Bit 8 MMCIS: MMC Interrupt Status

This bit is set high when Bit 11, Bit 10, or Bit 9 is set high. This bit is cleared only when all these bits are low. This bit is valid only when you select the Enable MAC Management Counters (MMC) option.

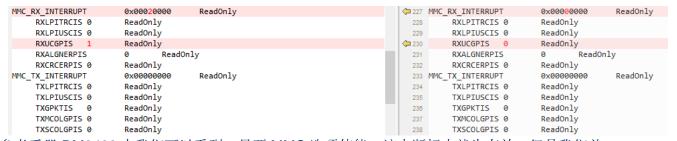

在两次三组寄存器的比较中,我们看到系统生成了 MMC 接收中断(MMC\_RX\_INTERRUPT 中RXUCGPIS)。这个符合前文的 MMCRXIS 和 MMCIS 的状态。

图 3 MMC RX INTERRUPT 的比较

从参考手册 RM0433 中我们可以看到,只要 MMC 选项使能,该中断标志就为有效。但是我们并 没有使能 MMC 选项,甚至我们都没有使能 MMC 中断,为什么还是有中断产生呢?

# MMC 中断的特点

MMC 选项其实是默认使能。我们可以从参考手册 RM0433 中看到这一点。

LAT1022 - Rev 0.3 page 2/7

#### 图 4 MAC management counters

### 58.5.10 MAC management counters

The counters in the MAC Management Counters (MMC) module can be viewed as an extension of the register address space of the CSR module. The MMC module maintains a set of registers for gathering statistics on the received and transmitted packets. The register set includes a control register for controlling the behavior of the registers, two 32-bit registers containing interrupts generated (receive and transmit), and two 32-bit registers containing masks for the Interrupt register (receive and transmit). These registers are accessible from the Application through the AHB slave interface in the same way the CSR registers are accessed. The organization of these registers is shown in Section 58.11.4: Ethernet MAC and MMC registers.

The MMC counters are free running. There is no separate enable for the counters to start. A particular MMC counter starts counting when corresponding packet is received or transmitted.

In addition to control registers, two sets of registers are implemented:

- 6 registers used for collision, error and good packets counters

- 4 registers to record LPI mode transition

在 MMC 默认使能的情况下,什么情况下会产生中断呢? 让我们在 RM0433 里搜索下两次寄存器比较发现的 RXUCGPIS 寄存器:

#### 图 5 RXUCGPIS

Bit 17 RXUCGPIS: MMC Receive Unicast Good Packet Counter Interrupt Status

This bit is set when the rxunicastpackets\_g counter reaches nalf of the maximum value or the maximum value.

我们可以看到 MMC 接收中断会在统计值最大的一半或者最大值时会产生。这也和 MMC RX interrupt register 开始的说明描述一致。

图 6 MMC Receive Interrupt 的条件

### MMC Rx interrupt register (ETH\_MMC\_RX\_INTERRUPT)

Address offset: 0x0704 Reset value: 0x0000 0000

This register maintains the interrupts generated from all Receive statistics counters.

The MMC Receive Interrupt register maintains the interrupts that are generated when the following occur:

- Receive statistic counters reach half of their maximum values (0x8000\_0000 for 32 bit counter and 0x8000 for 16 bit counter).

- Receive statistic counters cross their maximum values (0xFFFF\_FFFF for 32 bit counter and 0xFFFF for 16 bit counter).

综合这两点,我们可以认为,在长时间以太网收发包之后,MMC 中断几乎一定会发生。这符合客户案例的场景,例如,重现这个问题需要 7 到 8 天。当然从这里我们也可以推断出,我们如果

LAT1022 - Rev 0.3 page 3/7

加快测试数据包收发的发送,MMC 中断会发生更早。那么,如何避免在产品应用中这种问题发生呢?

## 解决方案

### 1.1. 使用 MMC 中断

MMC 中断是个有用的功能。如果我们要使用的话,可以参考 MMC Rx interrupt register (ETH\_MMC\_RX\_INTERRUPT)和 MMC Tx interrupt register (ETH\_MMC\_TX\_INTERRUPT)的 描述。我们需要对 MMC 进行一个读的操作。

Figure 7 MMC Receive Interrupt 清除的方法

### MMC Rx interrupt register (ETH\_MMC\_RX\_INTERRUPT)

Address offset: 0x0704

Reset value: 0x0000 0000

This register maintains the interrupts generated from all Receive statistics counters.

The MMC Receive Interrupt register maintains the interrupts that are generated when the following occur:

- Receive statistic counters reach half of their maximum values (0x8000\_0000 for 32 bit counter and 0x8000 for 16 bit counter).

- Receive statistic counters cross their maximum values (0xFFFF\_FFFF for 32 bit counter and 0xFFFF for 16 bit counter).

When the Counter Stop Rollover is set, interrupts are set but the counter remains at allones. The MMC Receive Interrupt register is a 32 bit register. An interrupt bit is cleared when the respective MMC counter that caused the interrupt is read in the least significant byte lane (Bits[7:0]) or the respective counter must be read to clear the interrupt bit.

以及

LAT1022 - Rev 0.3 page 4/7

#### Figure 8 MMC Transmit Interrupt register 清除的方法

### MMC Tx interrupt register (ETH\_MMC\_TX\_INTERRUPT)

Address offset: 0x0708

Reset value: 0x0000 0000

This register maintains the interrupts generated from all Transmit statistics counters.

The MMC Transmit Interrupt register maintains the interrupts generated when transmit statistic counters reach half their maximum values (0x8000\_0000 for 32 bit counter and 0x8000 for 16 bit counter), and when they cross their maximum values (0xFFF\_FFFF for 32-bit counter and 0xFFFF for 16-bit counter).

When Counter Stop Rollover is set, the interrupts are set but the counter remains at allones.

The MMC Transmit Interrupt register is a 32 bit register. An interrupt bit is cleared when the respective wind counter that caused the interrupt is read

The least significant byte lane (Bits[7]:0]) of the respective counter must be read to clear the interrupt bit.

这也解释了,客户为什么发现,通过调试器一个一个去读取以太网寄存器,会在某个操作时让异常状态恢复到正常。

## 1.2. 关闭 MMC 中断

在很多情况下,MMC 中断对实际产品没有意义。例如,在这个案例中,我们可以选择关闭 MMC 中断。这就需要用到 MMC 中断的 mask 寄存器:

- MMC Rx interrupt mask register (ETH\_MMC\_RX\_INTERRUPT\_MASK)

- MMC Tx interrupt mask register (ETH\_MMC\_TX\_INTERRUPT\_MASK)

我们可以添加以下代码到我们的应用代码里

ETH->MMCRIMR = ETH\_MMCRIMR\_RXLPITRCIM | ETH\_MMCRIMR\_RXLPIUSCIM |

ETH\_MMCRIMR\_RXUCGPIM | ETH\_MMCRIMR\_RXALGNERPIM | ETH\_MMCRIMR\_RXCRCERPIM;

ETH->MMCTIMR = ETH\_MMCTIMR\_TXLPITRCIM | ETH\_MMCTIMR\_TXLPIUSCIM |

ETH\_MMCTIMR\_TXGPKTIM | ETH\_MMCTIMR\_TXMCOLGPIM | ETH\_MMCTIMR\_TXSCOLGPIM;

客户反馈找不到 ETH 的定义。其实在 STM32H7 的例程里,我们可以很容易发现 ETH 定义在 STM32Cube\Repository\STM32Cube\_FW\_H7\_V1.8.0\Drivers\CMSIS\Device\ST\STM32H7xx\I nclude\stm32h750xx.h:

### #define ETH ((ETH\_TypeDef \*)ETH\_BASE)

也就是说,如果你的工程时源自 STM32Cube 例程,你应该能够加入以上代码并且能够成功运行。

在加入上述代码或者类似操作后,客户反馈,再次进行超过**7**天以上的压力测试,系统运行正常。

LAT1022 - Rev 0.3 page 5/7

# 总结

STM32H7的 MMC 中断需要加以注意,如果不使用 MMC,需要确保它已经关闭;否则在经过长时间网络收发后,系统会产生并不是用户期望的中断,导致系统假死。另外,我们也看到了调试 STM32 以太网的常规方式,也就是借助工具而不需要写代码就可以进行寄存器的比较。这种方法值得使用 STM32 以太网的用户进行调试时参考。

LAT1022 - Rev 0.3 page 6/7

### 版本历史

| 日期          | 版本  | 变更   |

|-------------|-----|------|

| 2021年10月29日 | 1.0 | 首版发布 |

|             |     |      |

|             |     |      |

### 重要通知 - 请仔细阅读

意法半导体公司及其子公司 ("ST") 保留随时对 ST 产品和 / 或本文档进行变更的权利, 恕不另行通知。买方在订货之前应获取关于 ST 产品的最新信息。 ST 产品的销售依照订单确认时的相关 ST 销售条款。

买方自行负责对 ST 产品的选择和使用, ST 概不承担与应用协助或买方产品设计相关的任何责任。

ST 不对任何知识产权进行任何明示或默示的授权或许可。

转售的 ST 产品如有不同于此处提供的信息的规定,将导致 ST 针对该产品授予的任何保证失效。

ST 和 ST 徽标是 ST 的商标。若需 ST 商标的更多信息,请参考 www.st.com/trademarks。所有其他产品或服务名称均为其 各自所有者的财产。

本文档是 ST 中国本地团队的技术性文章,旨在交流与分享,并期望借此给予客户产品应用上足够的帮助或提醒。若文中内容存有局限或与 ST 官网资料不一致,请以实际应用验证结果和 ST 官网最新发布的内容为准。您拥有完全自主权是否采纳本文档(包括代码,电路图等)信息,我们也不承担因使用或采纳本文档内容而导致的任何风险。

本文档中的信息取代本文档所有早期版本中提供的信息。

© 2020 STMicroelectronics - 保留所有权利

LAT1022 - Rev 0.3 page 7/7