# 开启嵌入式智能视觉应用新时代

莱迪思半导体

2021 年 3 月

## 开启嵌式智能视觉应用新时代

全球新冠疫情肆虐以及对提高安全性和效率的需求正促使各行业企业在其系统中集成智能嵌入式视觉技术，以支持人员侦测、非接触式人机交互和更强大的 AR/VR 功能，同时使用智能机器视觉技术来提高制造水平和产量。Allied Market Research 的数据显示，2019 年全球机器视觉系统市场规模为 297 亿美元，到 2027 年预计将达到 749 亿美元，2020 年到 2027 年的复合年增长率约为 11.3%。

作为Lattice低功耗嵌入式视觉系统解决方案集合，mVision使用了模块化硬件平台、IP构建模块、易于使用的FPGA设计工具、参考设计和演示以及定制设计服务网络，提供定制化的性能和灵活的接口互连(MIPI CSI-2、LVDS、PCIe、GigE)，并专为智能工厂、机器视觉、智慧城市和智能家居应用中的低功耗(150mW-1W)、小尺寸封装(2.5 x2.5mm-10x10mm)设计进行了优化，能应对传感器互连、桥接、聚合和图像信号处理等各类设计挑战。

### 牛刀小试

2020年3月，mVision 1.0解决方案面世，为需要快速构建原型系统的消费类嵌入式视觉设计人员提供了高度灵活、小型模块化的解决方案。其核心特点包括：

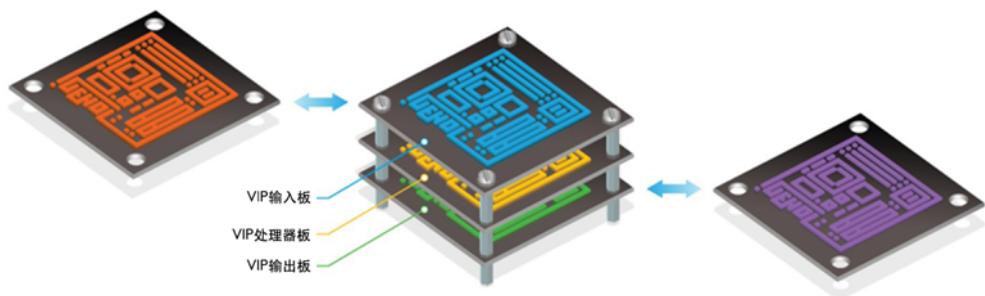

- 视频接口平台(VIP)——模块化硬件开发板，支持嵌入式视觉应用中常用的各种视频和I/O接口(包括MIPI、LVDS、DisplayPort、HDMI、USB等)。VIP开发板支持包括CrossLink™、ECP5™和基于莱迪思Nexus技术平台的CrossLink-NX FPGA。VIP通过简单的插拔即可轻松地实现输入和输出板互连，两个60引脚的高速板对板连接器用以减少物理连线，确保设计工程师可以复用现有经过验证的软硬件构建模块。

- 完善的IP库——mVision解决方案集合包括各类即时可用的IP核，可用于连接MIPI

和LVDS图像传感器、ISP、通用连接标准(例如USB、千兆以太网)和HDMI、DisplayPort、GigE Vision等显示标准。

- FPGA设计工具—可使用Lattice Diamond®和Lattice Radiant®这两款易于使用的FPGA设计工具。这些工具可以自动处理许多常见的设计任务，从而加速和简化莱迪思FPGA的编程。

- 端到端的参考设计—为进一步加速系统开发，莱迪思mVision为常见的嵌入式视觉应用提供了完整的参考设计，包括传感器桥接、传感器聚合和图像处理。

- 定制化设计服务—针对需要协助将其嵌入式视觉系统推向市场的客户，莱迪思建立了设计服务合作伙伴网络，可以满足从开发单独的功能设计模块到提供一站式交钥匙解决方案等一系列客户需求。

### mVision 2.0：从消费级到工业级

一年后的2021年3月，在mVision 1.0版本的基础上，Lattice推出了mVision 2.0。该方案新增了一些重要更新，包括对工业和汽车系统中使用的主流新型图像传感器的支持，以及全新图像信号处理IP核和参考设计，帮助开发人员设计网络边缘智能视觉应用。该解决方案集合现还支持Lattice Propel设计环境，可简化使用嵌入式RISC-V处理器的视觉系统的开发。

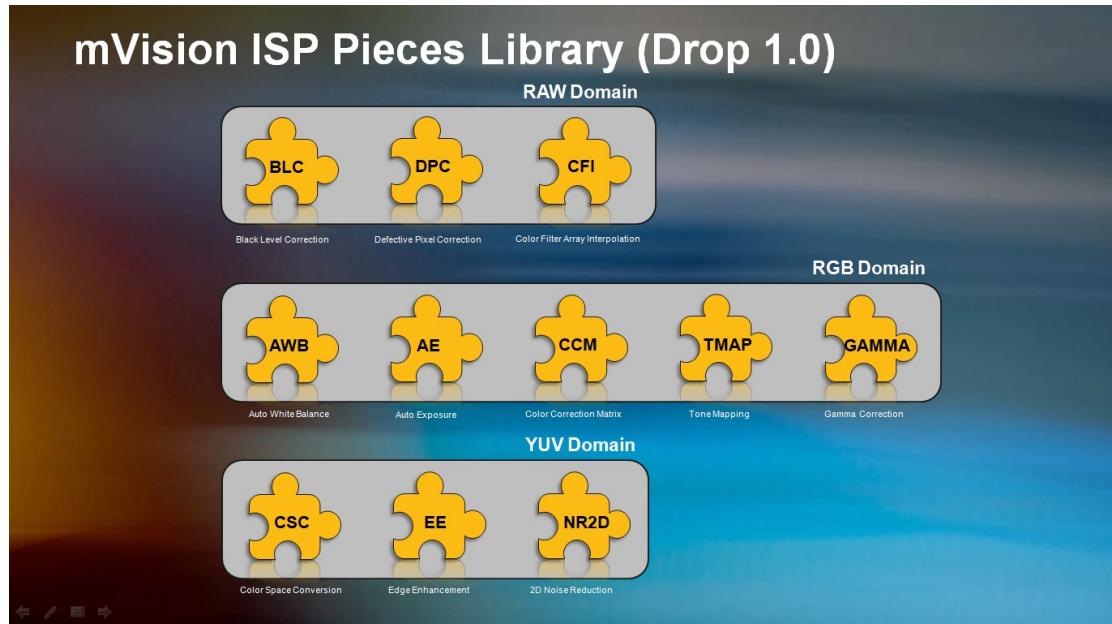

此外，mVision 2.0 ISP Pieces Library(Drop 1.0)还具备完整的ISP管道功能，支持高达150MHz的像素时钟(720p120/1080p60等)和高达96dB(16位)的场景动态范

围，提供定制 ISP 解决方案的灵活互连，用以平衡性能和成本。调试工具包则具备外部 DDR 存储器实时图像捕获功能，支持 Lattice SSP 注册访问工具包，能够针对特定环境进行调整。

mVision 2.0 解决方案集合的主要更新包括：

- 扩展了对汽车、工业和医疗领域嵌入式视觉应用的支持

与消费级嵌入式视觉方案不同，应用于工业、汽车和医疗领域的嵌入式视觉方案既要求低功耗、小尺寸，还对帧率准确度要求极为严苛，不允许丢帧现象发生。因此，莱迪思在 mVision 2.0 增加了全新的开发板，除了原有的 CrossLink、CrossLink-NX、ECP5 之外，还包括支持工业和医疗应用的主流图像传感器 Sony IMX464/IMX568 和安森美半导体的 AR0234CS，开发人员可通过 I2C、SPI 或其他接口对摄像机传感器进行配置和操作。

## New VIP Sensor Modules for Industrial/Medical/Auto

CUSTOM DESIGN SERVICES

REFERENCE DESIGNS & DEMOS

SOFTWARE TOOLS

IP CORES

HARDWARE PLATFORMS

### Video Interface Platform (VIP) – Portfolio

CrossLink VIP Input Bridge Board

CrossLink-NX VIP Input Bridge Board

DisplayPort VIP Input Board

HDMI VIP Input Board

HDMI VIP Output Bridge Board

DisplayPort VIP Output Board

USB3-GbE VIP I/O Board

MicroSD Card Adapter

ECP5 VIP Processor Board

Sony IMX464 1/1.8" 4MP MIPI NIR Enhanced Rolling Shutter Sensor

Sony IMX563 1/1.8" 3.1MP MIPI NIR Enhanced Global Shutter Sensor

OnSemi AR0234CS 1/2.6", 2MP MIPI Global Shutter Sensor

**Supported Interface Boards:**

MIPI | eDP | HDMI | GigE | USB3

**Supported Lattice FPGAs:**

ECP5 | CrossLink | CrossLink-NX

VIP Supports Multiple Boards

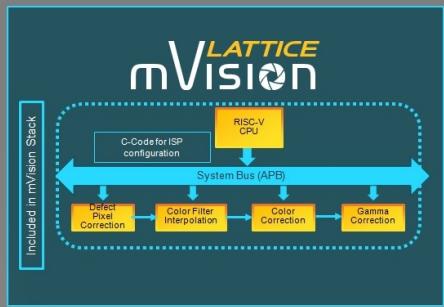

- 支持莱迪思 Propel 设计环境与 RISC-V 架构

Propel 是一款用于在低功耗、小尺寸莱迪思 FPGA 上加速基于嵌入式处理器开发的设计环境。该工具包括一套完整的图形和命令行工具，可创建、分析、编译和调试基于 FPGA 的处理器系统的硬件和软件设计。

而之所以新增对 RISC-V 架构的支持，其主要目的，一是希望通过使用 C 代码而非 RTL 语言的方式简便整个方案的配置；二是 RISC-V 作为开源方案，得到了大多数用户的 support。未来，Lattice 将计划在其他器件上逐步提供 RISC-V 软核支持。

## New Support for Software-based ISP Configuration

CUSTOM DESIGN SERVICES

REFERENCE DESIGNS & DEMOS

SOFTWARE TOOLS

IP CORES

HARDWARE PLATFORMS

**RISC-V**

ISP can be fully configured by modifying the included RISC-VC reference source code

**LATTICE PROPEL™**

Modify and test C Code

Drag-and-drop ISP IPs

**mVISION**

The diagram shows the mVISION stack architecture. It includes a RISC-V CPU at the top, connected to a System Bus (APB). The bus connects to a series of ISP processing blocks: Direct Pixel Correction, Color Filter Interpolation, Color Correction, and Gamma Correction. A dashed box labeled "Included in mVISION Stack" encloses the RISC-V CPU and the System Bus, indicating they are part of the stack.

- 全新莱迪思图像信号处理器(ISP)参考设计

以往的传感器产品都自带 ISP 驱动，但随着传感器复杂度的增加、分辨率的提升，传感器厂商很难调动一款受众面很广的驱动，因此往往不再提供 ISP 驱动，多数只提供传感或者原始数据，这部分工作就被渐渐转移给了方案开发者。Lattice 此次增加了专门的 ISP，为客户拓展了 mVision 解决方案的选择，可以帮助用户在产品设计中快速部署嵌入式视觉等应用提供便利。

**New Demos and Reference Designs**

**Bridging**

- NEW MIPI CSI-2 to OpenLDI LVDS Interface Bridge

- NEW N to 1 CSI-2/DSI Duplicator

- NEW subLVDS to MIPI CSI-2 Image Sensor Bridge

**Aggregation**

- NEW MIPI CSI-2 N to 1 Side-by-side Aggregation

- 4:1 Image Aggregation

- MIPI CSI-2 Virtual Channel Aggregation

**Image Processing**

- NEW Generic ISP

- NEW Customized ISP optimized for new sensors (2 Sony, 1 ON Semi)

ECP5      CrossLink      CrossLinkPlus      CrossLink-NX

- 新增图像信号处理与桥接聚合 IP

mVision 2.0 所包含的 IP 核主要分为四类：显示处理、图像信号处理、桥接和聚合、互连。其中，图像信号处理、桥接和聚合 IP 为新增项目，用户可以直接引入这些模块，减少从零开发的流程投入。同时，所有这些可用的 IP 模块都支持 CrossLink-NX。

**New and Optimized ISP Blocks**

**Display Processing**

- Color Space Conversion

- Scaler

- Overlay

- Video Frame Buffer

**Image Signal Processing**

- NEW & OPTIMIZED Detect Pixel Correction

- Color Filter Array

- Interpolation

- Black-level Correction

- Auto White Balance

- Auto Exposure

- Color Correction Matrix

**Bridging / Aggregation**

- CSI-2/DSI D-PHY Receiver

- CSI-2/DSI D-PHY Transmitter

- Byte-to-Pixel Converter

**Connectivity**

- Pixel-to-Byte Converter

- FPD-LINK Receiver

- FPD-LINK Transmitter

- DisplayPort Rx

- DisplayPort Tx

All Available IP Blocks Support CrossLink-NX

## 应用案例

从 M2M 应用中的工业显示系统、工业 4.0 解决方案，到高级驾驶辅助系统(ADAS)和车载信息娱乐系统，再到数码单反相机、无人机、机器人、虚拟现实(VR)系统和医疗设备，在当今所有行业中摄像头应用的数量都在不断增长，目标识别、深度感知、碰撞规避和决策制定等更加智能的应用也正在变为现实。

为了构建灵活、智能学习的环境，将理想变为现实，莱迪思携手 Softnautics、LogicFruit、Bitec、TATA、Helion 等合作伙伴开发出了数十种灵活的解决方案以满足当今嵌入式视觉设计工程师的需求，如不断变化的接口、低功耗图像信号处理和硬件加速。

- 使用 Helion IONOS ISP 加速产品上市进程

莱迪思与 Helion Vision 合作提供全面的解决方案，包括一系列图像信号处理产品系列，从基本的(ECO HD-ISP)到支持高级高动态范围图像处理(HDR HD-ISP)的产品。其中，Helion Vision 的 IONOS IP 系列通过 IP 库提供 100 多款独立 IP，实现即插即用的处理解决方案，并在此前专为 ECP3™ 和 ECP5™ 架构进行了优化的基础上，新增对 CrossLink-NX 的支持，可显着减少所需的 FPGA 资源和延迟。

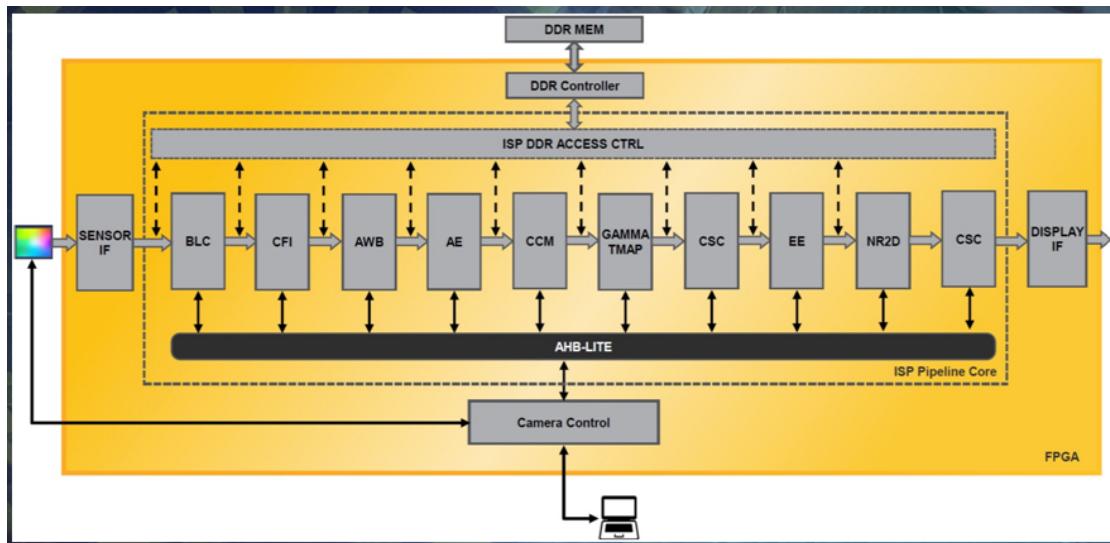

- 基于流水线架构的 mVision ISP 参考设计

下图展示的是一个基于流水线架构的完整的莱迪思 mVision ISP 参考设计，支持 Sony IMX464/IMX568 和安森美半导体的 AR0234CS 图像传感器，2020 年 11 月交付早期客户使用。最早使用的硬件平台为 ECP5，预计将于 2021 年第一季度内支持 CrossLink。根据规划，Lattice 最初的 ISP 参考设计将专注于工业、医疗和汽车应用，莱迪思会提供包含非常适合医疗、工业、航空航天、汽车和消费者应用的流行传感器在内的多种 EVDK 模块。

- Sony IMX464 VIP 传感器输入板

全新 Sony IMX464 VIP 传感器输入板包括 Sony 1/1.8" 4MP MIPI NIR 增强型卷帘快门传感器模块，以及连接 EVDK 的适配器数据线。与嵌入式视觉开发套件(EVDK)无缝连接，支持 2688(H) x 1520(V)分辨率、4 M 像素、最高 90 FPS、HDR 等性能指标，适用于监控、工厂自动化、工业摄像头应用。

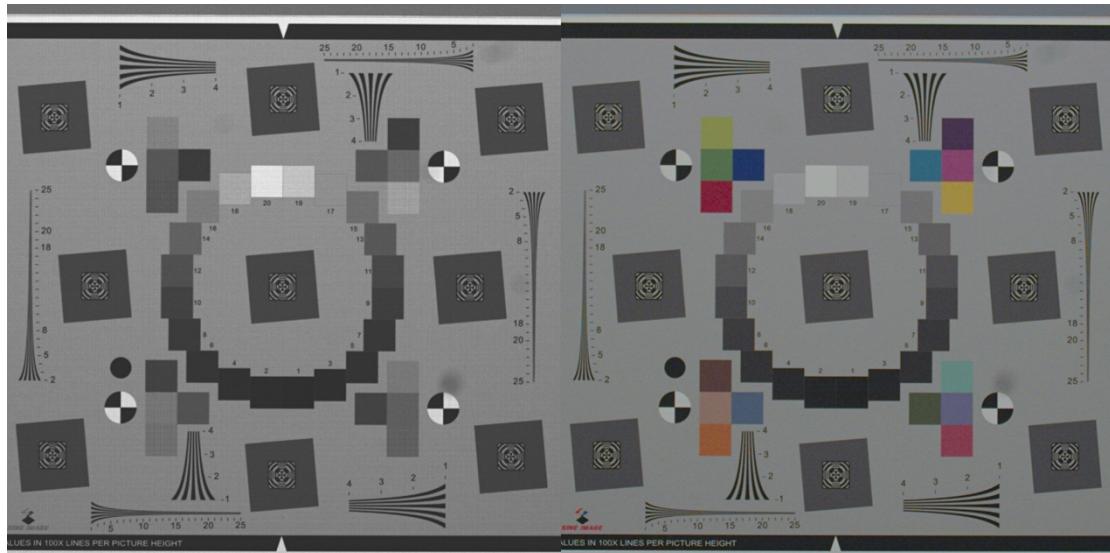

左图：未经 ISP 处理的图片；右图：经过 ISP 处理后的 RGB 图像

嵌入式视觉系统设计工程师面临着许多挑战，图像信号处理问题只是其中一项，上述案例也只是众多应用中的代表。图像传感器形式和尺寸各异，并且在像素粒度、信噪比、光敏度和色深方面的性能等级也不同。此外，照明和物体的色彩对比度等环境因素进一步让系统设计变得更加复杂。这些情况往往会对系统设计工程师带来严重的问题。

题，因为他们要实时地进行图像预处理。要解决产品设计周期延长和风险上升的问题，莱迪思在图像处理领域具备的专业经验将能够很好的帮助他们应对上述挑战。