# UltraScale FPGAs Transceivers Wizard v1.7

# LogiCORE IP Product Guide

**Vivado Design Suite**

PG182 (v1.7) November 11, 2019

# **Table of Contents**

#### **IP Facts**

| Chapter 1: Overview                                 |

|-----------------------------------------------------|

| Feature Summary 5                                   |

| Applications                                        |

| Licensing and Ordering Information 6                |

| Chapter 2: Product Specification                    |

| Wizard Basic Concepts                               |

| Performance                                         |

| Resource Utilization                                |

| Port Descriptions                                   |

| Chapter 3: Designing with the Core                  |

| General Design Guidelines 59                        |

| Reset Controller Helper Block                       |

| Transmitter User Clocking Network Helper Block      |

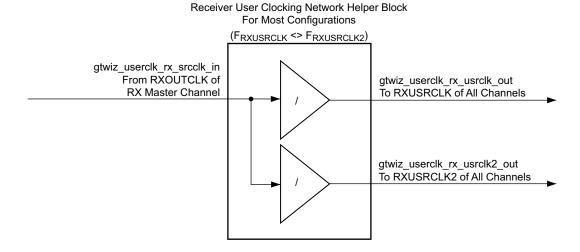

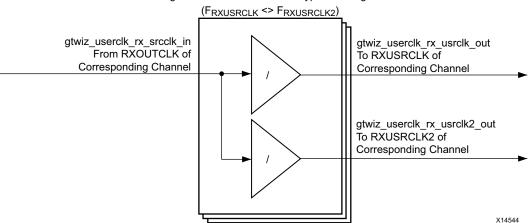

| Receiver User Clocking Network Helper Block         |

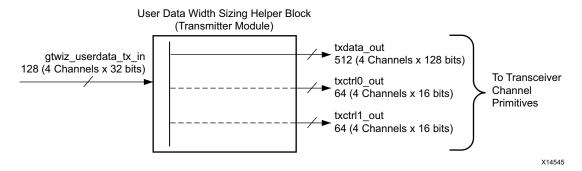

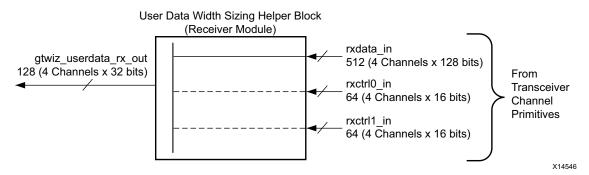

| User Data Width Sizing Helper Block 73              |

| Transmitter Buffer Bypass Controller Helper Block74 |

| Receiver Buffer Bypass Controller Helper Block 76   |

| Transceiver Common Primitive                        |

| Chapter 4: Design Flow Steps                        |

| Customizing and Generating the Core 80              |

| Constraining the Core 97                            |

| Simulation                                          |

| Synthesis and Implementation                        |

| Chapter 5: Example Design                           |

| Purpose of the Example Design 103                   |

| Hierarchy and Structure 104                         |

| Link Status and Initialization                      |

| VIO Core Instance                                  | . 110 |

|----------------------------------------------------|-------|

| In-System IBERT Core Instance                      | . 112 |

| Convenience Features                               | . 113 |

| Adapting the Example Design                        | . 115 |

| Limitations of the Example Design                  | . 116 |

| Chapter 6: Test Bench                              |       |

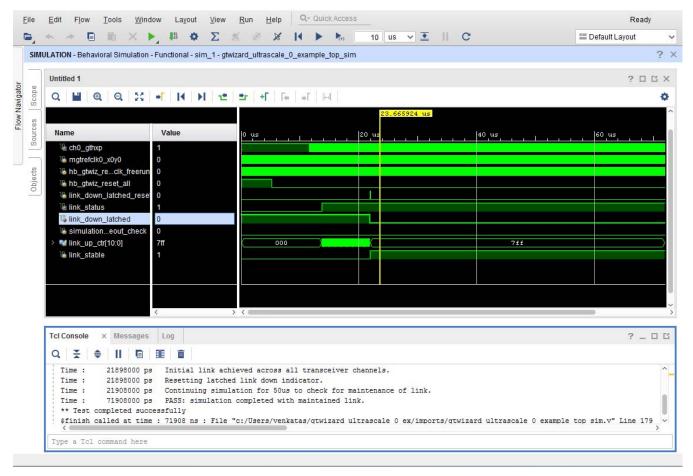

| Simulating the Example Design                      | . 117 |

| Simulation Behavior                                | . 118 |

| Appendix A: Migrating and Upgrading                |       |

| Migrating to the Vivado Design Suite               | . 120 |

| Upgrading from a Previous Version                  | . 120 |

| Migrating from a Previous Device Family            | . 121 |

| Appendix B: Debugging                              |       |

| Finding Help on Xilinx.com                         | . 122 |

| Vivado Design Suite Debug Feature                  | . 123 |

| Appendix C: Additional Resources and Legal Notices |       |

| Xilinx Resources                                   | . 124 |

| References                                         | . 124 |

| Revision History                                   | . 125 |

| Please Read: Important Legal Notices               | . 129 |

#### Introduction

The UltraScale™ FPGAs Transceivers Wizard IP core helps configure one or more serial transceivers. You can target an industry standard using provided configuration presets, or start from scratch. The flexible Transceivers Wizard generates a customized IP core for the transceivers, configuration options, and enabled ports you have selected, optionally including a variety of helper blocks to simplify common functionality. In addition, the wizard can produce an example design for simple simulation and hardware usage demonstration.

#### **Features**

- Transceiver configuration presets for industry standards

- Simple and intuitive feature selection flow

- Automatically sets transceiver parameters

- Advanced options to tune performance

- Transceiver site and reference clock selection interface

- Available helper blocks to simplify common or complex transceiver usage

- Optional exposure of any transceiver port depending upon the selected configuration

- Example design with configurable PRBS generator, checker, and link status indicator to demonstrate functionality in simulation and hardware

- Flexible placement of each helper block: within core for simplicity, or within example design for user customization

- Support for UltraScale and UltraScale+™ architectures

| LogiCORE™ IP Facts Table                  |                                                                             |  |  |  |  |  |

|-------------------------------------------|-----------------------------------------------------------------------------|--|--|--|--|--|

|                                           | Core Specifics                                                              |  |  |  |  |  |

| Supported<br>Device Family <sup>(1)</sup> | UltraScale+™ Families<br>Kintex® UltraScale FPGA<br>Virtex® UltraScale FPGA |  |  |  |  |  |

| Supported User<br>Interfaces              | Not Applicable                                                              |  |  |  |  |  |

| Resources                                 | See Table 2-2.                                                              |  |  |  |  |  |

|                                           | Provided with Core                                                          |  |  |  |  |  |

| Design Files                              | RTL                                                                         |  |  |  |  |  |

| Example Design                            | Verilog                                                                     |  |  |  |  |  |

| Test Bench                                | Verilog                                                                     |  |  |  |  |  |

| Constraints File                          | Xilinx Design Constraints (XDC)                                             |  |  |  |  |  |

| Simulation<br>Model                       | Source HDL with SecureIP transceiver simulation models                      |  |  |  |  |  |

| Supported<br>S/W Driver                   | Not Provided                                                                |  |  |  |  |  |

|                                           | Tested Design Flows                                                         |  |  |  |  |  |

| Design Entry                              | Vivado® Design Suite                                                        |  |  |  |  |  |

| Simulation                                | For supported simulators, see the Xilinx Design Tools: Release Notes Guide. |  |  |  |  |  |

| Synthesis                                 | Vivado Synthesis                                                            |  |  |  |  |  |

| Support                                   |                                                                             |  |  |  |  |  |

| Release Notes<br>and Known<br>Issues      | Master Answer Record: 57487                                                 |  |  |  |  |  |

| All Vivado IP<br>Change Logs              | Master Vivado IP Change Logs: 72775                                         |  |  |  |  |  |

|                                           | Xilinx Support web page                                                     |  |  |  |  |  |

#### Notes:

For a complete list of supported devices, see the Vivado IP catalog.

## Overview

The UltraScale™ FPGAs Transceivers Wizard is used to configure and simplify the use of one or more serial transceivers in a Xilinx® UltraScale or UltraScale+™ device. See Chapter 2, Product Specification for a detailed description of the core.

This document describes the Wizard IP core. See the *UltraScale Architecture GTH Transceivers User Guide* (UG576) [Ref 1] or *UltraScale Architecture GTY Transceivers User Guide* (UG578) [Ref 2] for details on the specific use and behavior of the serial transceivers.

## **Feature Summary**

The wizard provides the following features:

- Customization flow driven by the Vivado Integrated Design Environment (IDE), providing high-level choices that configure supported transceiver features and automatically set primitive parameters, as appropriate

- Variety of transceiver configuration preset selections to target industry standards

- Advanced configuration options to tune transceiver performance

- Transceiver site, reference clock, and recovered clock selection interface for enabling one or more transceiver channels and adherence to clock routing restrictions

- Optional feature configuration interface for comma detection and alignment, channel bonding, clock correction, buffer control, advanced clocking, and some protocol-specific features

- Available helper blocks to simplify common or complex transceiver usage, and the choice to either include or exclude each helper block from the core

- Helper blocks excluded from the core are delivered as user-customizable starting points within the example design

- Ability to locate enabled transceiver common primitives either within the core or in the example design, and connectivity to simplify resource sharing across multiple cores

- Optional port enablement interface provides the ability to expose any transceiver primitive port as a top-level core port. However, these ports should not be in conflict with any dependent helper core location and configuration of the wizard.

- Synthesizable example design with configurable pseudo-random binary sequence (PRBS) data generator, checker, and link status indicator logic to quickly demonstrate core and transceiver functionality in simulation and hardware:

- Simulation test bench that monitors example design PRBS lock in loopback, and indicates resulting link status

- Virtual input/output (VIO) core instance that simplifies basic example design hardware bring-up, and key debug signal probing

- Additional convenience features, including differential reference clock buffer instantiation and wiring, and per-channel vector slicing

- Core and example design level Xilinx design constraints (XDC) files with timing, location, and other constraints as necessary for the selected configuration

### **Applications**

The wizard is the supported method of configuring and using one or more serial transceivers in a Xilinx UltraScale FPGA.

### **Licensing and Ordering Information**

This Xilinx LogiCORE™ IP module is provided at no additional cost with the Xilinx Vivado Design Suite under the terms of the Xilinx End User License. Information about this and other Xilinx LogiCORE IP modules is available at the Xilinx Intellectual Property page. For information about pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your local Xilinx sales representative.

# **Product Specification**

The UltraScale™ FPGAs Transceivers Wizard core is the supported method of configuring and using one or more serial transceivers in a Xilinx® UltraScale or UltraScale+™ device. In addition to automatically setting primitive parameters as appropriate for your application, the wizard simplifies serial transceiver usage by providing a variety of port enablement and helper block convenience functions. These concepts, as well as technical specifications, are described in this chapter.

## **Wizard Basic Concepts**

**Transceiver primitives**. Fundamentally, the wizard instantiates, configures, and connects one or more serial transceiver primitives to provide a simplified user interface to those resources. The core instance configures the channel and common primitives by applying HDL parameter values derived from the Vivado® Integrated Design Environment (IDE)-driven customization of that instance.

**Transceiver configuration presets**. During Vivado IDE-driven customization, you can choose from a variety of transceiver configuration presets to target an industry standard. If required, customization settings can be further modified to suit your application.

**Optional port enablement**. Xilinx serial transceiver primitives have many ports, and most ports are usually not required for any one use mode. The wizard provides access to all transceiver primitive ports using an optional port enablement interface, but by default offers a compact user interface by exposing only those ports likely to be necessary for the core as customized. Some of the ports might not be applicable to be exposed from GT wizard core due to the customization and optional enablement of some of the helper cores.

**Helper blocks**. The wizard provides optional modules called helper blocks that abstract or automate certain common or complex transceiver usage procedures. Each helper block can be located either within the core or outside it. They are delivered with the example design as a user-modifiable starting point. Helper blocks in this release include:

- Reset controller. Controls and abstracts the transceiver reset sequence.

- *Transmitter user clocking network.* Contains resources to drive the transmitter user clocking network.

- Receiver user clocking network. Contains resources to drive the receiver user clocking network.

- *User data width sizing*. Sizes the transmitter and receiver data vectors to the specified user widths.

- *Transmitter buffer bypass controller.* Controls and abstracts the transmitter buffer bypass procedure, if required.

- Receiver buffer bypass controller. Controls and abstracts the receiver buffer bypass procedure, if required.

The wizard is intended to simplify the use of the serial transceivers. However, it is still important to understand the behavior, usage, and any limitations of the transceivers. See the *UltraScale Architecture GTH Transceivers User Guide* (UG576) [Ref 1] or *UltraScale Architecture GTY Transceivers User Guide* (UG578) [Ref 2] for details.

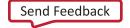

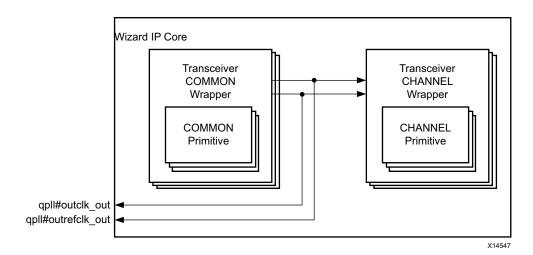

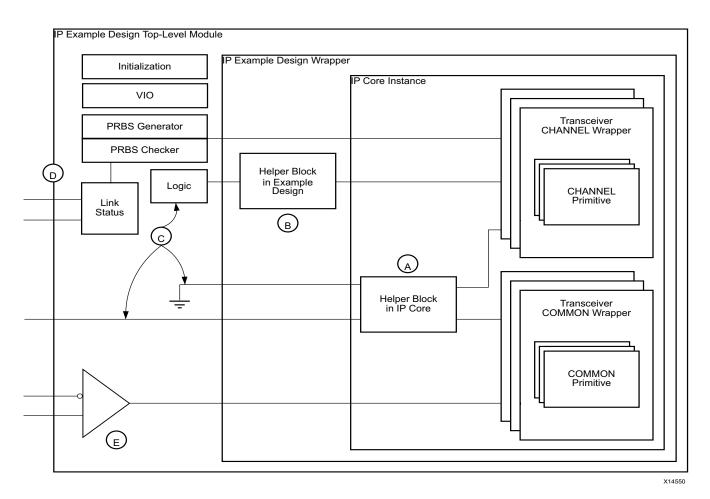

Figure 2-1 and its description illustrate the basic concepts of the wizard in the context of the core hierarchy.

Figure 2-1: Wizard IP Core Block Diagram

Transceiver channel primitives and transceiver common primitives are instantiated by the transceiver channel wrapper and transceiver common wrapper modules, respectively. One or more wrapper modules can be used to instantiate those transceiver primitives as required for your application. The wrapper modules apply appropriate parameter values to the underlying transceiver primitives based on the choices made during IP customization, or according to the selected transceiver configuration preset. These wrappers, like the rest of the core hierarchy, should not be user-modified.

To provide a compact user interface, only those transceiver primitive ports that are likely needed for the selected configuration are exposed as wizard IP core-level ports by default. Input vector **A** represents an enabled core port that drives a corresponding input port of one or more transceiver channel primitives. Likewise, output vector **A'** is driven by a corresponding output port of one or more transceiver common primitives. If not enabled by default, user-required ports can be individually enabled during IP customization for maximum flexibility.

Transceiver primitive input ports that are not exposed through the core boundary are tied off to their appropriate values (per the core customization) within the Vivado Design Suite IP core wrapper. Net **B** represents an input port of one or more transceiver channel primitives that is not enabled as a core port and is automatically tied Low by the wizard. Net **B**' represents an analogous transceiver common primitive input, tied High.

The wizard provides optional helper blocks to simplify common or complex transceiver usage, and each helper block can be located either within the core or within the user-modifiable example design. Vector **C** represents the simple user interface of the optional helper blocks when located within the core, while nets **D** represents the more complex interface between those helper blocks and the transceiver channel and/or common primitives to which they connect.

#### **Performance**

The wizard is designed to operate in coordination with the performance characteristics of the transceiver primitives it instantiates.

#### **Maximum Frequencies**

For the serial transceiver switching characteristics and the serial transceiver user clock switching characteristics, see the applicable data sheet for your device:

- Kintex UltraScale Architecture Data Sheet: DC and AC Switching Characteristics (DS892) [Ref 3]

- Virtex UltraScale Architecture Data Sheet: DC and AC Switching Characteristics (DS893) [Ref 4]

- Zynq UltraScale+ MPSoC Data Sheet: DC and AC Switching Characteristics (DS925) [Ref 5]

- Kintex UltraScale+ FPGAs Data Sheet: DC and AC Switching Characteristics (DS922) [Ref 6]

- Virtex UltraScale+ FPGA Data Sheet: DC and AC Switching Characteristics (DS923) [Ref 7]

You must use the frequency ranges specified by these documents for proper transceiver and core operation.

IMPORTANT: A free-running clock input, gtwiz\_reset\_clk\_freerun\_in, is required by the reset controller helper block to reset the transceiver primitives. In GTH transceiver core configurations targeting engineering sample (ES1 or ES2) UltraScale devices and GTHE4, GTYE4 UltraScale+ devices where the CPLL is used, this clock must also drive each bit of the drpclk\_in port. As shown in Table 2-1, the maximum frequency of this clock must not exceed either an upper bound or the slowest of the transceiver channels' user clock frequencies for the core as customized. The precise frequency of the free-running clock which is specified during IP customization should not change because of the dependencies in the CPLL calibration block. For more details, see Chapter 4, Customizing and Generating the Core. The free-running clock must not be derived from user clocks or their sources.

Table 2-1: Free-Running Clock Maximum Frequency

| Transceiver User Clock Frequency Relationship   | Maximum Frequency of gtwiz_reset_clk_freerun_in                          |

|-------------------------------------------------|--------------------------------------------------------------------------|

| $F_{RXUSRCLK2} \le F_{TXUSRCLK2}$               | The lower of F <sub>UPPER</sub> <sup>(1)</sup> or F <sub>RXUSRCLK2</sub> |

| F <sub>RXUSRCLK2</sub> > F <sub>TXUSRCLK2</sub> | The lower of F <sub>UPPER</sub> <sup>(1)</sup> or F <sub>TXUSRCLK2</sub> |

#### Notes:

#### Other Performance Characteristics

See the *UltraScale Architecture GTH Transceivers User Guide* (UG576) [Ref 1] or *UltraScale Architecture GTY Transceivers User Guide* (UG578) [Ref 2] for other performance characteristics of the transceiver primitives. Also, see the following datasheets for any other device level details:

- Kintex UltraScale Architecture Data Sheet: DC and AC Switching Characteristics (DS892)

[Ref 3]

- Virtex UltraScale Architecture Data Sheet: DC and AC Switching Characteristics (DS893) [Ref 4]

- Kintex UltraScale+ FPGAs Data Sheet: DC and AC Switching Characteristics (DS922) [Ref 6]

- Virtex UltraScale+ FPGA Data Sheet: DC and AC Switching Characteristics (DS923)

[Ref 7]

- Zynq UltraScale+ MPSoC Data Sheet: DC and AC Switching Characteristics (DS925)

[Ref 5]

#### **Resource Utilization**

The basic Wizard HDL is highly structural and uses a negligible amount of device resources to instantiate and wire the transceiver primitives for use. In GTH transceiver configurations targeting engineering sample (ES1 or ES2) UltraScale devices where the CPLL is used as either the transmitter PLL type, receiver PLL type, or as the source of a selectable TXOUTCLK frequency, CPLL calibration logic is included. One BUFG\_GT and approximately 280 LUTs and 285 flip-flops are utilized per enabled transceiver channel in these configurations.

The device utilization of the optional helper blocks is shown in Table 2-2. These resources are only consumed when the relevant helper block is enabled and used within the core, or otherwise included in your design. Resources are shown per helper block instance, although most configurations that enable a helper block use only one instance.

<sup>1.</sup> F<sub>UPPER</sub> is 200 MHz for GTH transceiver core configurations targeting engineering sample (ES1 or ES2) UltraScale devices where the CPLL is used; or 250 MHz for other configurations. For UltraScale+ devices, this is 250 MHz.

Table 2-2: Resource Utilization of Helper Blocks

| Helper Bloc                          | Device Resources (per Helper Block Instance)   |      |            |                  |

|--------------------------------------|------------------------------------------------|------|------------|------------------|

| Туре                                 | Configuration                                  | LUTs | Flip-Flops | Clock Buffers    |

| Reset controller                     | Any                                            | 120  | 195        | 0 <sup>(1)</sup> |

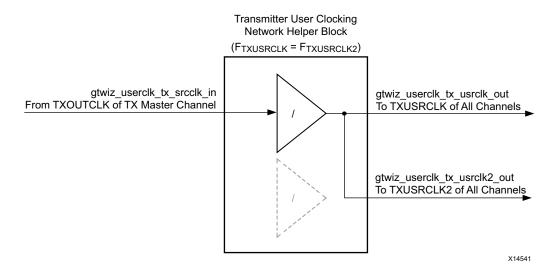

| Transmitter user clocking network    | $F_{TXUSRCLK} = F_{TXUSRCLK2}$                 | 0    | 2          | 1 (BUFG_GT)      |

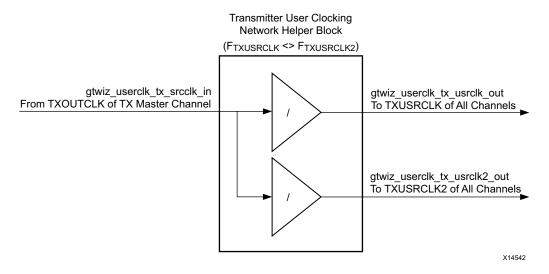

| mansimiter user clocking network     | F <sub>TXUSRCLK</sub> ≠ F <sub>TXUSRCLK2</sub> | 0    | 2          | 2 (BUFG_GT)      |

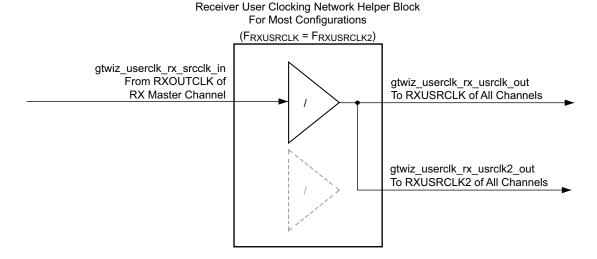

| Receiver user clocking network       | F <sub>RXUSRCLK</sub> = F <sub>RXUSRCLK2</sub> | 0    | 2          | 1 (BUFG_GT)      |

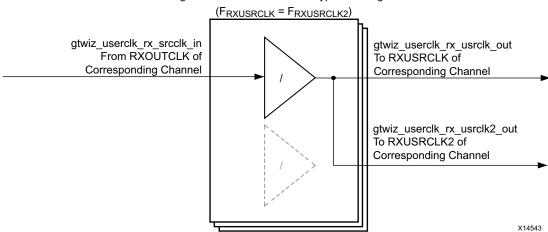

| Receiver user clocking network       | F <sub>RXUSRCLK</sub> ≠ F <sub>RXUSRCLK2</sub> | 0    | 2          | 2 (BUFG_GT)      |

| Transmitter buffer bunges controller | Single-lane                                    | 8    | 25         | 0                |

| Transmitter buffer bypass controller | Multi-lane                                     | <20  | 25         | 0                |

| Descriver buffer bunges controller   | Single-lane                                    | 8    | 25         | 0                |

| Receiver buffer bypass controller    | Multi-lane                                     | <20  | 25         | 0                |

| User data width sizing               | Any                                            | 0    | 0          | 0                |

#### Notes:

Resources required are derived from post-synthesis reports and may change during implementation.

#### **Port Descriptions**

The wizard enables access to underlying transceiver primitive ports as needed, as well as providing a user interface to enable the helper blocks that are included within the core instance. As such, the wizard user interface can vary significantly between different customizations.

To provide a compact interface, only those transceiver primitive ports that are likely needed for the selected customization are exposed as Wizard IP core-level ports. Additional user-required ports can be individually enabled during IP customization using a flexible optional port enablement interface. See Chapter 4, Customizing and Generating the Core, for details on optional port enablement.

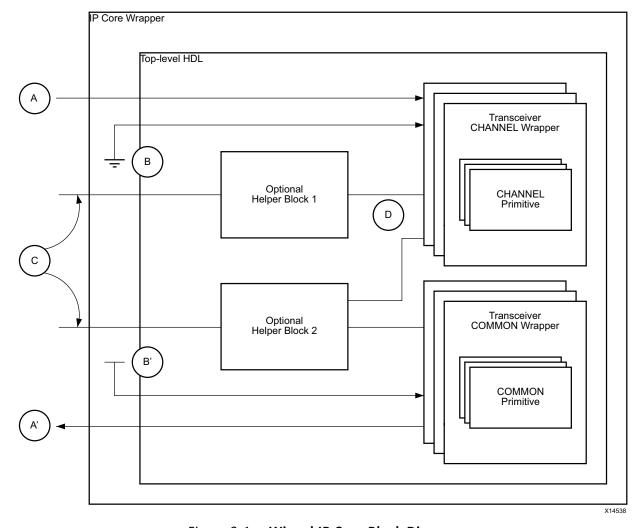

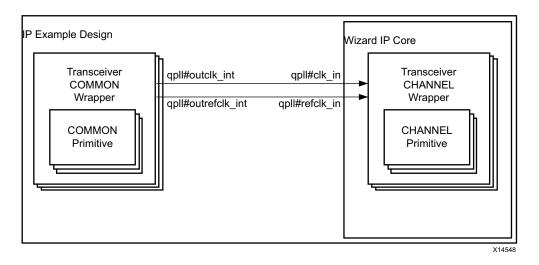

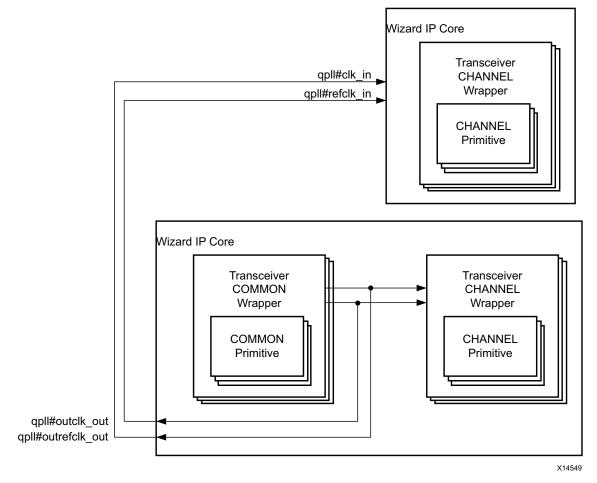

The presence and location of helper blocks also affects the core user interface. When a helper block is enabled and located within the core, a simple user interface is available at the core boundary instead of at the transceiver primitive ports to which it connects. When the helper block is located within the example design, the more complex transceiver primitive ports it connects to are necessarily enabled at the core boundary. Figure 2-2 illustrates how helper block location affects core port enablement.

<sup>1.</sup> A shareable BUFG for the free-running clock is not included in the helper block HDL.

Figure 2-2: Effect of Port Helper Block Location on Port Enablement

#### **Reset Controller Helper Block Ports**

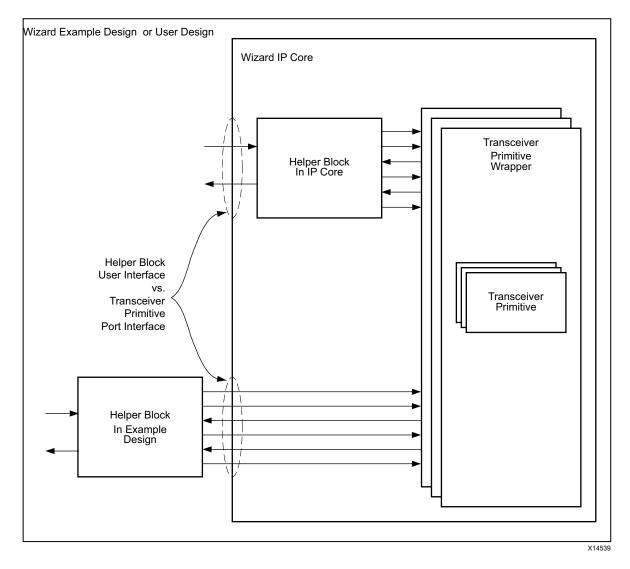

The reset controller helper block contains a user interface and a transceiver interface. The user interface provides a simple means of initiating and monitoring the completion of transceiver reset procedures. The transceiver interface implements the signaling required to control the various transceiver primitive reset sequences.

Reset controller helper block user interface ports can be identified by the prefix *gtwiz\_reset\_*. For guidance on the usage of the reset controller helper block, see Chapter 3, Designing with the Core.

The reset controller helper block user interface ports described in Table 2-3 are present on the Wizard IP core instance when it is configured to locate the reset controller helper block in the core. They are also present on the helper block itself, directly accessible when the helper block is located in the example design.

Table 2-3: Reset Controller Helper Block User Interface Ports on Core (Helper Block in Core)

| Name                                   | Direction | Width | Clock Domain | Description                                                                                                                                                                                                                                            |

|----------------------------------------|-----------|-------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gtwiz_reset_clk_freerun_in             | Input     | 1     |              | Free-running clock used to reset transceiver primitives. Must be toggling prior to device configuration. See Performance, page 10 for maximum frequency guidance.                                                                                      |

| gtwiz_reset_all_in                     | Input     | 1     | Async        | User signal to reset the phase-locked loops (PLLs) and active data directions of transceiver primitives. The falling edge of an active-High, asynchronous pulse of at least one gtwiz_reset_clk_freerun_in period in duration initializes the process. |

| gtwiz_reset_tx_pll_and_dat<br>apath_in | Input     | 1     | Async        | User signal to reset the transmit data direction and associated PLLs of transceiver primitives. An active-High, asynchronous pulse of at least one gtwiz_reset_clk_freerun_in period in duration initializes the process.                              |

| gtwiz_reset_tx_datapath_in             | Input     | 1     | Async        | User signal to reset the transmit data direction of transceiver primitives. An active-High, asynchronous pulse of at least one gtwiz_reset_clk_freerun_in period in duration initializes the process.                                                  |

Table 2-3: Reset Controller Helper Block User Interface Ports on Core (Helper Block in Core)

| Name                                   | Direction | Width               | Clock Domain                         | Description                                                                                                                                                                                                              |

|----------------------------------------|-----------|---------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gtwiz_reset_rx_pll_and_dat<br>apath_in | Input     | 1                   | Async                                | User signal to reset the receive data direction and associated PLLs of transceiver primitives. An active-High, asynchronous pulse of at least one gtwiz_reset_clk_freerun_in period in duration initializes the process. |

| gtwiz_reset_rx_datapath_in             | Input     | 1                   | Async                                | User signal to reset the receive data direction of transceiver primitives. An active-High, asynchronous pulse of at least one gtwiz_reset_clk_freerun_in period in duration initializes the process.                     |

| gtwiz_reset_rx_cdr_stable_<br>out      | Output    | 1                   | gtwiz_reset_clk_<br>freerun_in       | Active-High indication that the clock and data recovery (CDR) circuits of the transceiver primitives are stable. Reserved; do not use.                                                                                   |

| gtwiz_reset_qpll0lock_in               | Input     | 1 × Num.<br>commons | Async                                | QPLL0 lock signal, present when<br>the transceiver common is<br>located in the example design<br>and QPLL0 is used as either the<br>transmitter or receiver PLL type.                                                    |

| gtwiz_reset_qpll1lock_in               | Input     | 1 × Num.<br>commons | Async                                | QPLL1 lock signal, present when<br>the transceiver common is<br>located in the example design<br>and QPLL1 is used as either the<br>transmitter or receiver PLL type.                                                    |

| gtwiz_reset_tx_done_out                | Output    | 1                   | TXUSRCLK2 of<br>TX master<br>channel | Active-High indication that the transmitter reset sequence of transceiver primitives as initiated by the reset controller helper block has completed.                                                                    |

| gtwiz_reset_rx_done_out                | Output    | 1                   | RXUSRCLK2 of<br>RX master<br>channel | Active-High indication that the receiver reset sequence of transceiver primitives as initiated by the reset controller helper block has completed.                                                                       |

Table 2-3: Reset Controller Helper Block User Interface Ports on Core (Helper Block in Core)

| Name                       | Direction | Width               | Clock Domain                   | Description                                                                                                                                                |

|----------------------------|-----------|---------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gtwiz_reset_qpll0reset_out | Output    | 1 × Num.<br>commons | gtwiz_reset_clk_<br>freerun_in | QPLL0 reset signal, present when the transceiver common is located in the example design and QPLL0 is used as either the transmitter or receiver PLL type. |

| gtwiz_reset_qpll1reset_out | Output    | 1 × Num.<br>commons | gtwiz_reset_clk_<br>freerun_in | QPLL1 reset signal, present when the transceiver common is located in the example design and QPLL1 is used as either the transmitter or receiver PLL type. |

The reset controller helper block user interface ports described in Table 2-4 are present on the core instance when it is configured to locate the reset controller helper block in the example design.

Table 2-4: Reset Controller Helper Block User Interface Ports on Core (Helper Block in Example Design)

| Name                   | Direction | Width | Clock<br>Domain | Description                                                                                                                                                                                                                      |

|------------------------|-----------|-------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gtwiz_reset_tx_done_in | Input     | 1     | Async           | Upon successful completion of the transmitter reset sequence, this active-High port must be asserted to allow dependent helper blocks within the core to operate. The reset controller helper block drives this port by default. |

| gtwiz_reset_rx_done_in | Input     | 1     | Async           | Upon successful completion of the receiver reset sequence, this active-High port must be asserted to allow dependent helper blocks within the core to operate. The reset controller helper block drives this port by default.    |

The reset controller helper block user interface ports described in Table 2-5 are not present on the core instance, but are present on the reset controller helper block itself when it is included in the example design.

Table 2-5: Other Reset Controller Helper Block User Interface Ports (Helper Block in Example Design)

| Name                                 | Direction | Width | Clock<br>Domain | Description                                                                                                                                                                                                                                                             |

|--------------------------------------|-----------|-------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gtwiz_reset_userclk_tx<br>_active_in | Input     | 1     | Async           | When the TXUSRCLK and TXUSRCLK2 signals that drive transceiver primitives are active and stable, this active-High port must be asserted for the transmitter reset sequence to complete. The transmitter user clocking network helper block drives this port by default. |

| gtwiz_reset_userclk_rx<br>_active_in | Input     | 1     | Async           | When the RXUSRCLK and RXUSRCLK2 signals that drive transceiver primitives are active and stable, this active-High port must be asserted to allow the receiver reset sequence to complete. The receiver user clocking network helper block drives this port by default.  |

The reset controller helper block transceiver interface ports described in Table 2-6 connect the reset controller helper block to transceiver primitives. When the helper block is located within the core, these connections are internal and the transceiver primitive inputs that are driven by helper block outputs cannot be enabled as optional ports on the core instance. Inversely, when the helper block is located in the example design, the connections cross the core boundary so the transceiver primitive ports that connect to the helper block are enabled by necessity.

**Table 2-6:** Reset Controller Helper Block Transceiver Interface Ports

| Name           | Direction | Width | Clock Domain | Description                                                                                                          |

|----------------|-----------|-------|--------------|----------------------------------------------------------------------------------------------------------------------|

| gtpowergood_in | Input     | 1     | Async        | Logical AND of all<br>GTPOWERGOOD signals<br>produced by transceiver channel<br>logic.                               |

| txusrclk2_in   | Input     | 1     |              | TXUSRCLK2 of master transceiver channel.                                                                             |

| plllock_tx_in  | Input     | 1     | Async        | Logical AND of all lock signals produced by PLLs that clock the transmit datapath of transceiver channel primitives. |

| txresetdone_in | Input     | 1     | Async        | Logical AND of all TXRESETDONE signals produced by transceiver channel primitives.                                   |

| rxusrclk2_in   | Input     | 1     |              | RXUSRCLK2 of master transceiver channel.                                                                             |

| plllock_rx_in  | Input     | 1     | Async        | Logical AND of all lock signals produced by PLLs that clock the receive datapath of transceiver channel primitives.  |

Table 2-6: Reset Controller Helper Block Transceiver Interface Ports (Cont'd)

| Name               | Direction | Width | Clock Domain                                        | Description                                                                                                                               |

|--------------------|-----------|-------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| rxcdrlock_in       | Input     | 1     | Async                                               | Logical AND of all RXCDRLOCK signals produced by transceiver channel primitives.                                                          |

| rxresetdone_in     | Input     | 1     | Async                                               | Logical AND of all<br>RXRESETDONE signals produced<br>by transceiver channel<br>primitives.                                               |

| pllreset_tx_out    | Output    | 1     | gtwiz_reset_clk_freerun_in<br>(used asynchronously) | Active-High signal fanned out to<br>the reset ports of all PLLs that<br>clock the transmit datapath of<br>transceiver channel primitives. |

| txprogdivreset_out | Output    | 1     | gtwiz_reset_clk_freerun_in<br>(used asynchronously) | Active-High signal fanned out to TXPROGDIVRESET port of all transceiver channel primitives.                                               |

| gttxreset_out      | Output    | 1     | gtwiz_reset_clk_freerun_in<br>(used asynchronously) | Active-High signal fanned out to GTTXRESET port of all transceiver channel primitives.                                                    |

| txuserrdy_out      | Output    | 1     | gtwiz_reset_clk_freerun_in<br>(used asynchronously) | Active-High signal fanned out to TXUSERRDY port of all transceiver channel primitives.                                                    |

| pllreset_rx_out    | Output    | 1     | gtwiz_reset_clk_freerun_in<br>(used asynchronously) | Active-High signal fanned out to<br>the reset ports of all PLLs that<br>clock the receive datapath of<br>transceiver channel primitives.  |

| rxprogdivreset_out | Output    | 1     | gtwiz_reset_clk_freerun_in<br>(used asynchronously) | Active-High signal fanned out to RXPROGDIVRESET port of all transceiver channel primitives.                                               |

| gtrxreset_out      | Output    | 1     | gtwiz_reset_clk_freerun_in<br>(used asynchronously) | Active-High signal fanned out to GTRXRESET port of all transceiver channel primitives.                                                    |

| rxuserrdy_out      | Output    | 1     | gtwiz_reset_clk_freerun_in<br>(used asynchronously) | Active-High signal fanned out to RXUSERRDY port of all transceiver channel primitives.                                                    |

**Note:** All input/output ports which are described as async, are synchronized to gtwiz\_reset\_clk\_freerun\_in in the example design. In user designs, all asynchronous signals coming as inputs to the IP, should be asserted for sufficient time. This ensures that the synchronizers present inside the IP sampling on the gtwiz\_reset\_clk\_freerun\_in identify the toggles on these ports.

The reset controller helper block ports described in Table 2-7 must be tied off. By default, appropriate tie-offs are provided for each core customization.

Table 2-7: Reset Controller Helper Block Tie-off Ports

| Name              | Direction | Width | Clock Domain               | Description                                                                                                  |

|-------------------|-----------|-------|----------------------------|--------------------------------------------------------------------------------------------------------------|

| tx_enabled_tie_in | Input     | 1     | gtwiz_reset_clk_freerun_in | When tied High, transmitter resources are reset as part of the sequence in response to gtwiz_reset_all_in.   |

| rx_enabled_tie_in | Input     | 1     | gtwiz_reset_clk_freerun_in | When tied High, receiver resources are reset as part of the sequence in response to gtwiz_reset_all_in.      |

| shared_pll_tie_in | Input     | 1     | gtwiz_reset_clk_freerun_in | When tied High, the shared PLL is reset only once as part of the sequence in response to gtwiz_reset_all_in. |

#### **Transmitter User Clocking Network Helper Block Ports**

The transmitter user clocking network helper block provides a single interface with a source clock input port driven by a transceiver primitive-based output clock. Transmitter user clocking network helper block ports can be identified by the prefix <code>gtwiz\_userclk\_tx\_</code>. For guidance on the usage of the transmitter user clocking network helper block, see Chapter 3, <code>Designing</code> with the Core.

The transmitter user clocking network helper block ports described in Table 2-8 are present on the Wizard IP core instance when it is configured to locate the transmitter user clocking network helper block in the core.

Table 2-8: Transmitter User Clocking Network Helper Block Ports on Core (Helper Block in Core)

| Name                        | Direction | Width | Clock Domain | Description                                                                                                                                                  |

|-----------------------------|-----------|-------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gtwiz_userclk_tx_reset_in   | Input     | 1     | Async        | User signal to reset the clocking resources within the helper block. The active-High assertion should remain until gtwiz_userclk_tx_srcclk_in/out is stable. |

| gtwiz_userclk_tx_srcclk_out | Output    | 1     |              | Transceiver primitive-based clock source used to derive and buffer TXUSRCLK and TXUSRCLK2 outputs.                                                           |

| gtwiz_userclk_tx_usrclk_out | Output    | 1     |              | Drives TXUSRCLK of transceiver channel primitives. Derived from gtwiz_userclk_tx_srcclk_in/out, buffered and divided as necessary by BUFG_GT primitive.      |

Table 2-8: Transmitter User Clocking Network Helper Block Ports on Core (Helper Block in Core)

| Name                         | Direction | Width | Clock Domain                     | Description                                                                                                                                                          |

|------------------------------|-----------|-------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gtwiz_userclk_tx_usrclk2_out | Output    | 1     |                                  | Drives TXUSRCLK2 of transceiver channel primitives. Derived from gtwiz_userclk_tx_srcclk_in/out, buffered and divided as necessary by BUFG_GT primitive if required. |

| gtwiz_userclk_tx_active_out  | Output    | 1     | gtwiz_userclk_<br>tx_usrclk2_out | Active-High indication that the clocking resources within the helper block are not held in reset.                                                                    |

The transmitter user clocking network helper block ports described in Table 2-9 are present on the core instance when it is configured to locate the transmitter user clocking network helper block in the example design.

Table 2-9: Transmitter User Clocking Network Helper Block User Interface Ports on Core (Helper Block in Example Design)

| Name                       | Direction | Width | Clock<br>Domain | Description                                                                                                                                                                                                                                                                                                |

|----------------------------|-----------|-------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gtwiz_userclk_tx_active_in | Input     | 1     | Async           | When the clocks produced by the transmitter user clocking network helper block are active, this active-High port must be asserted to allow dependent helper blocks within the core to operate. The transmitter user clocking network helper block drives this port by default.                             |

| gtwiz_userclk_tx_reset_in  | Input     | 1     | Async           | This core port is present in GTH transceiver configurations targeting engineering sample (ES1 or ES2) UltraScale devices where the CPLL is used. It must be driven identically to the gtwiz_userclk_tx_reset_in port on the transmitter user clocking network helper block, present in the example design. |

The transmitter user clocking network helper block ports described in Table 2-10 are not present on the core instance but are present on the transmitter user clocking network helper block itself when it is included in the example design.

Table 2-10: Other Transmitter User Clocking Network Helper Block User Interface Ports (Helper Block in Example Design)

| Name                       | Direction | Width | Clock<br>Domain | Description                                                                                        |

|----------------------------|-----------|-------|-----------------|----------------------------------------------------------------------------------------------------|

| gtwiz_userclk_tx_srcclk_in | Input     | 1     |                 | Transceiver primitive-based clock source used to derive and buffer TXUSRCLK and TXUSRCLK2 outputs. |

#### **Receiver User Clocking Network Helper Block Ports**

The receiver user clocking network helper block provides a single interface with a source clock input port driven by a transceiver primitive-based output clock. Receiver user clocking network helper block ports can be identified by the prefix <code>gtwiz\_userclk\_rx\_</code>. For guidance on the usage of the receiver user clocking network helper block, see Chapter 3, Designing with the Core.

The receiver user clocking network helper block ports described in Table 2-11 are present on the wizard core instance when it is configured to locate the receiver user clocking network helper block in the core.

Table 2-11: Receiver User Clocking Network Helper Block Ports on Core (Helper Block in Core)

| Name                         | Direction | Width | Clock Domain                     | Description                                                                                                                                                          |

|------------------------------|-----------|-------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gtwiz_userclk_rx_reset_in    | Input     | 1     | Async                            | User signal to reset the clocking resources within the helper block. The active-High assertion should remain until gtwiz_userclk_rx_srcclk_in/out is stable.         |

| gtwiz_userclk_rx_srcclk_out  | Output    | 1     |                                  | Transceiver primitive-based clock source used to derive and buffer the RXUSRCLK and RXUSRCLK2 outputs.                                                               |

| gtwiz_userclk_rx_usrclk_out  | Output    | 1     |                                  | Drives RXUSRCLK of transceiver channel primitives. Derived from gtwiz_userclk_rx_srcclk_in/out, buffered and divided as necessary by BUFG_GT primitive.              |

| gtwiz_userclk_rx_usrclk2_out | Output    | 1     |                                  | Drives RXUSRCLK2 of transceiver channel primitives. Derived from gtwiz_userclk_rx_srcclk_in/out, buffered and divided as necessary by BUFG_GT primitive if required. |

| gtwiz_userclk_rx_active_out  | Output    | 1     | gtwiz_userclk_rx_<br>usrclk2_out | Active-High indication that the clocking resources within the helper block are not held in reset.                                                                    |

The receiver user clocking network helper block ports described in Table 2-12 are present on the core instance when it is configured to locate the receiver user clocking network helper block in the example design.

Table 2-12: Receiver User Clocking Network Helper Block User Interface Ports on Core (Helper Block in Example Design)

| Name                       | Direction | Width | Clock<br>Domain | Description                                                                                                                                                                                                                                                              |

|----------------------------|-----------|-------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gtwiz_userclk_rx_active_in | Input     | 1     | Async           | When the clocks produced by the receiver user clocking network helper block are active, this active-High port must be asserted to allow dependent helper blocks within the core to operate. The receiver user clocking network helper block drives this port by default. |

The receiver user clocking network helper block ports described in Table 2-13 are not present on the core instance, but are present on the receiver user clocking network helper block itself when it is included in the example design.

Table 2-13: Other Receiver User Clocking Network Helper Block User Interface Ports (Helper Block in Example Design)

| Name                       | Direction | Width | Clock<br>Domain | Description                                                                                        |

|----------------------------|-----------|-------|-----------------|----------------------------------------------------------------------------------------------------|

| gtwiz_userclk_rx_srcclk_in | Input     | 1     |                 | Transceiver primitive-based clock source used to derive and buffer RXUSRCLK and RXUSRCLK2 outputs. |

#### **User Data Width Sizing Helper Block Ports**

The user data width sizing helper block consists of two modules: one for the transmitter user data interface, and the other for the receiver user data interface. Each module contains a user interface and a transceiver interface. The user interface provides a single vector sized to user data width and scaled by the number of transceiver channels. The transceiver interface implements the bit assignments and any interleaving or de-interleaving required for interfacing to the data transmission and reception ports on the transceiver channel primitives.

User data width sizing helper block user interface ports can be identified by the prefix *gtwiz\_userdata\_*. See Chapter 3, Designing with the Core, for information about the user data width sizing helper block. The user and transceiver interfaces of the helper block transmitter and receiver modules are described in Table 2-14 through Table 2-17.

Table 2-14: User Data Width Sizing Helper Block User Interface Ports (Transmitter Module)

| Name                 | Direction | Width                                 | Clock Domain              | Description                                                                   |

|----------------------|-----------|---------------------------------------|---------------------------|-------------------------------------------------------------------------------|

| gtwiz_userdata_tx_in | Input     | TX user data width ×<br>Num. channels | TXUSRCLK2, per<br>channel | User interface<br>for data to be<br>transmitted by<br>transceiver<br>channels |

Table 2-15: User Data Width Sizing Helper Block User Interface Ports (Receiver Module)

| Name                  | Direction | Width                                 | Clock Domain              | Description                                                          |

|-----------------------|-----------|---------------------------------------|---------------------------|----------------------------------------------------------------------|

| gtwiz_userdata_rx_out | Output    | RX user data width ×<br>Num. channels | RXUSRCLK2, per<br>channel | User interface<br>for data<br>received by<br>transceiver<br>channels |

Table 2-16: User Data Width Sizing Helper Block Transceiver Interface Ports (Transmitter Module)

| Name        | Direction | Width               | Clock Domain           | Description                                           |

|-------------|-----------|---------------------|------------------------|-------------------------------------------------------|

| txdata_out  | Output    | 128 × Num. channels | TXUSRCLK2, per channel | Connects to TXDATA on transceiver channel primitives  |

| txctrl0_out | Output    | 16 × Num. channels  | TXUSRCLK2, per channel | Connects to TXCTRL0 on transceiver channel primitives |

| txctrl1_out | Output    | 16 × Num. channels  | TXUSRCLK2, per channel | Connects to TXCTRL1 on transceiver channel primitives |

Table 2-17: User Data Width Sizing Helper Block Transceiver Interface Ports (Receiver Module)

| Name        | Direction | Width               | Clock Domain           | Description                                           |

|-------------|-----------|---------------------|------------------------|-------------------------------------------------------|

| rxdata_in   | Input     | 128 × Num. channels | RXUSRCLK2, per channel | Connects to RXDATA on transceiver channel primitives  |

| rxctrl0_out | Input     | 16 × Num. channels  | RXUSRCLK2, per channel | Connects to RXCTRL0 on transceiver channel primitives |

| rxctrl1_out | Input     | 16 × Num. channels  | RXUSRCLK2, per channel | Connects to RXCTRL1 on transceiver channel primitives |

#### **Transmitter Buffer Bypass Controller Helper Block Ports**

The transmitter buffer bypass controller helper block contains a user interface and a transceiver interface. The user interface provides a simple means of initiating and monitoring the status of the transceiver transmitter buffer bypass procedure. The

transceiver interface implements the signaling required to control the transceiver primitive buffer bypass sequence.

Transmitter buffer bypass helper block user interface ports can be identified by the prefix *gtwiz\_buffbypass\_tx\_*. For guidance on the usage of the transmitter buffer bypass controller helper block, see Chapter 3, Designing with the Core.

The transmitter buffer bypass controller helper block user interface ports described in Table 2-18 are present on the Wizard IP core instance when it is configured to locate the transmitter buffer bypass controller helper block in the core. The ports are also present on the helper block itself, directly accessible when the helper block is located in the example design.

In this configuration, the helper block clock port <code>gtwiz\_buffbypass\_tx\_clk\_in</code> is driven internal to the core by the same source that drives <code>TXUSRCLK2</code> of the transmitter master channel, and is not exposed.

Table 2-18: Transmitter Buffer Bypass Controller Helper Block User Interface Ports on Core (Helper Block in Core)

| Name                              | Direction | Width | Clock Domain                   | Description                                                                                                                                                                       |

|-----------------------------------|-----------|-------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gtwiz_buffbypass_tx_reset_in      | Input     | 1     | gtwiz_buffbypass_<br>tx_clk_in | User signal to reset the logic within the helper block. An active-High, synchronous pulse should be provided immediately after TXUSRCLK2 stabilizes for all transceiver channels. |

| gtwiz_buffbypass_tx_start_user_in | Input     | 1     | gtwiz_buffbypass_<br>tx_clk_in | Active-High user signal that is synchronously pulsed to force the transmitter buffer bypass procedure to restart. Hold Low when not used.                                         |

| gtwiz_buffbypass_tx_done_out      | Output    | 1     | gtwiz_buffbypass_<br>tx_clk_in | Active-High indicates that the transmitter buffer bypass procedure has completed.                                                                                                 |

| gtwiz_buffbypass_tx_error_out     | Output    | 1     | gtwiz_buffbypass_<br>tx_clk_in | Active-High indicates that the transmitter buffer bypass helper block encountered an error condition.                                                                             |

The transmitter buffer bypass controller helper block user interface ports described in Table 2-19 are not present on the core instance but are present on the transmitter buffer bypass controller helper block when it is included in the example design.

Table 2-19: Other Transmitter Buffer Bypass Controller Helper Block User Interface Ports (Helper Block in Example Design)

| Name                             | Direction | Width | Clock<br>Domain | Description                                                                                                                                                                                         |

|----------------------------------|-----------|-------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gtwiz_buffbypass_tx_clk_in       | Input     | 1     |                 | Transceiver primitive-based clock used to control the transmitter buffer bypass controller helper block. Must be driven by the same source that drives TXUSRCLK2 of the transmitter master channel. |

| gtwiz_buffbypass_tx_resetdone_in | Input     | 1     | Async           | Active-High indicates that transmitter reset sequence has completed, which allows the buffer bypass procedure to begin.                                                                             |

The transmitter buffer bypass controller helper block transceiver interface ports (described in Table 2-20) connect the transmitter buffer bypass controller helper block to transceiver primitives. When the helper block is located within the core, these connections are internal, and the transceiver primitive inputs that are driven by helper block outputs cannot be enabled as optional ports on the core instance. Inversely, when the helper block is located in the example design, the connections cross the core boundary, and the transceiver primitive ports that connect to the helper block are enabled by necessity.

To implement the multi-lane buffer bypass procedure, the port width of each signal scales with the number of transceiver channels that the transmitter buffer bypass controller helper block interfaces to.

Table 2-20: Transmitter Buffer Bypass Controller Helper Block Transceiver Interface Port

| Name               | Direction | Width                | Clock Domain | Description                                                   |

|--------------------|-----------|----------------------|--------------|---------------------------------------------------------------|

| txphaligndone_in   | Input     | 1 × Num.<br>channels | Async        | Connects to TXPHALIGNDONE of transceiver channel primitives   |

| txphinitdone_in    | Input     | 1 × Num.<br>channels | Async        | Connects to TXPHINITDONE of transceiver channel primitives    |

| txdlysresetdone_in | Input     | 1 × Num.<br>channels | Async        | Connects to TXDLYSRESETDONE of transceiver channel primitives |

| txsyncout_in       | Input     | 1 × Num.<br>channels | Async        | Connects to TXSYNCOUT of transceiver channel primitives       |

Table 2-20: Transmitter Buffer Bypass Controller Helper Block Transceiver Interface Port

| Name              | Direction | Width                | Clock Domain                                        | Description                                                 |

|-------------------|-----------|----------------------|-----------------------------------------------------|-------------------------------------------------------------|

| txsyncdone_in     | Input     | 1 × Num.<br>channels | Async                                               | Connects to TXSYNCDONE of transceiver channel primitives    |

| txphdlyreset_out  | Output    | 1 × Num.<br>channels | Tied off                                            | Connects to TXPHDLYRESET of transceiver channel primitives  |

| txphalign_out     | Output    | 1 × Num.<br>channels | Tied off                                            | Connects to TXPHALIGN of transceiver channel primitives     |

| txphalignen_out   | Output    | 1 × Num.<br>channels | Tied off                                            | Connects to TXPHALIGNEN of transceiver channel primitives   |

| txphdlypd_out     | Output    | 1 × Num.<br>channels | Tied off                                            | Connects to TXPHDLYPD of transceiver channel primitives     |

| txphinit_out      | Output    | 1 × Num.<br>channels | Tied off                                            | Connects to TXPHINIT of transceiver channel primitives      |

| txphovrden_out    | Output    | 1 × Num.<br>channels | Tied off                                            | Connects to TXPHOVRDEN of transceiver channel primitives    |

| txdlysreset_out   | Output    | 1 × Num.<br>channels | gtwiz_buffbypass_tx_clk_in<br>(used asynchronously) | Connects to TXDLYSRESET of transceiver channel primitives   |

| txdlybypass_out   | Output    | 1 × Num.<br>channels | Tied off                                            | Connects to TXDLYBYPASS of transceiver channel primitives   |

| txdlyen_out       | Output    | 1 × Num.<br>channels | Tied off                                            | Connects to TXDLYEN of transceiver channel primitives       |

| txdlyovrden_out   | Output    | 1 × Num.<br>channels | Tied off                                            | Connects to TXDLYOVRDEN of transceiver channel primitives   |

| txphdlytstclk_out | Output    | 1 × Num.<br>channels | Tied off                                            | Connects to TXPHDLYTSTCLK of transceiver channel primitives |

of transceiver channel

primitives

| Name            | Direction | Width                | <b>Clock Domain</b> | Description                                               |

|-----------------|-----------|----------------------|---------------------|-----------------------------------------------------------|

| txdlyhold_out   | Output    | 1 × Num.<br>channels | Tied off            | Connects to TXDLYHOLD of transceiver channel primitives   |

| txdlyupdown_out | Output    | 1 × Num.<br>channels | Tied off            | Connects to TXDLYUPDOWN of transceiver channel primitives |

| txsyncmode_out  | Output    | 1 × Num.<br>channels | Tied off            | Connects to TXSYNCMODE of transceiver channel primitives  |

| txsyncallin_out | Output    | 1 × Num.<br>channels | Async               | Connects to TXSYNCALLIN of transceiver channel primitives |

| txsyncin_out    | Output    | 1 × Num.             | Async               | Connects to TXSYNCIN                                      |

Table 2-20: Transmitter Buffer Bypass Controller Helper Block Transceiver Interface Port

#### **Receiver Buffer Bypass Controller Helper Block Ports**

channels

The receiver buffer bypass controller helper block contains a user interface and a transceiver interface. The user interface provides a simple means of initiating and monitoring the status of the transceiver receiver buffer bypass procedure. The transceiver interface implements the signaling required to control the transceiver primitive buffer bypass sequence.

Receiver buffer bypass helper block user interface ports can be identified by the prefix *gtwiz\_buffbypass\_rx\_*. For guidance on the usage of the receiver buffer bypass controller helper block, see Chapter 3, Designing with the Core.

The receiver buffer bypass controller helper block user interface ports described in Table 2-21 are present on the Wizard IP core instance when it is configured to locate the receiver buffer bypass controller helper block in the core. The ports are also present on the helper block itself, directly accessible when the helper block is located in the example design.

In this configuration, the helper block clock port <code>gtwiz\_buffbypass\_rx\_clk\_in</code> is driven internal to the core by the same source that drives <code>RXUSRCLK2</code> of the receiver master channel, and is therefore not exposed. When the single-lane buffer bypass procedure is used, one instance of the helper block exists per transceiver channel. The width of each port scales by this factor, and each helper block instance is clocked by the same source that drives <code>RXUSRCLK2</code> of the associated channel.

Table 2-21: Receiver Buffer Bypass Controller Helper Block User Interface Ports on Core (Helper Block in Core)

| Name                              | Direction | Width | Clock Domain                   | Description                                                                                                                                                                       |

|-----------------------------------|-----------|-------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gtwiz_buffbypass_rx_reset_in      | Input     | 1     | gtwiz_buffbypass_<br>rx_clk_in | User signal to reset the logic within the helper block. An active-High, synchronous pulse should be provided immediately after RXUSRCLK2 stabilizes for all transceiver channels. |

| gtwiz_buffbypass_rx_start_user_in | Input     | 1     | gtwiz_buffbypass_<br>rx_clk_in | Active-High user signal that is synchronously pulsed to force the receiver buffer bypass procedure to restart. Hold Low when not used.                                            |

| gtwiz_buffbypass_rx_done_out      | Output    | 1     | gtwiz_buffbypass_<br>rx_clk_in | Active-High indicates that the receiver buffer bypass procedure has completed.                                                                                                    |

| gtwiz_buffbypass_rx_error_out     | Output    | 1     | gtwiz_buffbypass_<br>rx_clk_in | Active-High indicates that the receiver buffer bypass helper block encountered an error condition.                                                                                |

The receiver buffer bypass controller helper block user interface ports described in Table 2-22 are not present on the core instance but are present on the receiver buffer bypass controller helper block itself when it is included in the example design.

Table 2-22: Other Receiver Buffer Bypass Controller Helper Block User Interface Ports (Helper Block in Example Design)

| Name                             | Direction | Width | Clock<br>Domain | Description                                                                                                                                                                                   |

|----------------------------------|-----------|-------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gtwiz_buffbypass_rx_clk_in       | Input     | 1     |                 | Transceiver primitive-based clock used to control the receiver buffer bypass controller helper block. Must be driven by the same source that drives RXUSRCLK2 of the receiver master channel. |

| gtwiz_buffbypass_rx_resetdone_in | Input     | 1     | Async           | Active-High indication that receiver reset sequence has completed, which allows the buffer bypass procedure to begin.                                                                         |

The receiver buffer bypass controller helper block transceiver interface ports described in Table 2-23 connect the receiver buffer bypass controller helper block to transceiver primitives. When the helper block is located within the core, these connections are internal,

and the transceiver primitive inputs that are driven by helper block outputs cannot be enabled as optional ports on the core instance. Inversely, when the helper block is located in the example design, the connections cross the core boundary, so the transceiver primitive ports that connect to the helper block are enabled by necessity.

To implement the multi-lane buffer bypass procedure, the width of each port scales with the number of transceiver channels that the receiver buffer bypass controller helper block interfaces to. When the single-lane buffer bypass procedure is used, one instance of the helper block exists per transceiver channel, so the scaling factor is 1.

Table 2-23: Receiver Buffer Bypass Controller Helper Block Transceiver Interface Ports

| Name               | Direction | Width                | Clock Domain                                        | Description                                                   |

|--------------------|-----------|----------------------|-----------------------------------------------------|---------------------------------------------------------------|

| rxphaligndone_in   | Input     | 1 × Num.<br>channels | Async                                               | Connects to RXPHALIGNDONE of transceiver channel primitives   |

| rxdlysresetdone_in | Input     | 1 × Num.<br>channels | Async                                               | Connects to RXDLYSRESETDONE of transceiver channel primitives |

| rxsyncout_in       | Input     | 1 × Num.<br>channels | Async                                               | Connects to RXSYNCOUT of transceiver channel primitives       |

| rxsyncdone_in      | Input     | 1 × Num.<br>channels | Async                                               | Connects to RXSYNCDONE of transceiver channel primitives      |

| rxphdlyreset_out   | Output    | 1 × Num.<br>channels | Tied off                                            | Connects to RXPHDLYRESET of transceiver channel primitives    |

| rxphalign_out      | Output    | 1 × Num.<br>channels | Tied off                                            | Connects to RXPHALIGN of transceiver channel primitives       |

| rxphalignen_out    | Output    | 1 × Num.<br>channels | Tied off                                            | Connects to RXPHALIGNEN of transceiver channel primitives     |

| rxphdlypd_out      | Output    | 1 × Num.<br>channels | Tied off                                            | Connects to RXPHDLYPD of transceiver channel primitives       |

| rxphovrden_out     | Output    | 1 × Num.<br>channels | Tied off                                            | Connects to RXPHOVRDEN of transceiver channel primitives      |

| rxdlysreset_out    | Output    | 1 × Num.<br>channels | gtwiz_buffbypass_rx_clk_in<br>(used asynchronously) | Connects to RXDLYSRESET of transceiver channel primitives     |

transceiver channel

primitives

| Name            | Direction | Width                | <b>Clock Domain</b> | Description                                               |

|-----------------|-----------|----------------------|---------------------|-----------------------------------------------------------|

| rxdlybypass_out | Output    | 1 × Num.<br>channels | Tied off            | Connects to RXDLYBYPASS of transceiver channel primitives |

| rxdlyen_out     | Output    | 1 × Num.<br>channels | Tied off            | Connects to RXDLYEN of transceiver channel primitives     |

| rxdlyovrden_out | Output    | 1 × Num.<br>channels | Tied off            | Connects to RXDLYOVRDEN of transceiver channel primitives |

| rxsyncmode_out  | Output    | 1 × Num.<br>channels | Tied off            | Connects to RXSYNCMODE of transceiver channel primitives  |

| rxsyncallin_out | Output    | 1 × Num.<br>channels | Async               | Connects to RXSYNCALLIN of transceiver channel primitives |

| rxsyncin_out    | Output    | 1 × Num.             | Tied off            | Connects to RXSYNCIN of                                   |

Table 2-23: Receiver Buffer Bypass Controller Helper Block Transceiver Interface Ports (Cont'd)

#### **Transceiver Common Ports**

A subset of the ports (described in Table 2-24) is present on the wizard core instance when it is configured with one or more active transceiver common primitives, and when those primitives are located within the core. These ports connect through the core hierarchy to the corresponding transceiver common primitive ports. Because only a subset is required for a given core customization, most are not exposed as ports on the core interface by default. See Chapter 4, Customizing and Generating the Core, for details on optional port enablement.

channels

The width of each port scales with the number of transceiver common primitives instantiated within the core instance. The least significant bit(s) correspond to the first enabled transceiver common primitive in increasing grid order, where the Y axis increments before X. For example, the QPLLOREFCLKSEL port on a transceiver common primitive is 3 bits in size. In a hypothetical Wizard IP core customization that instantiates three GTH transceiver common primitives in physical positions GTHE3\_COMMON\_X0Y2, GTHE3\_COMMON\_X0Y5, and GTHE3\_COMMON\_X1Y3, the qpllorefclksel\_in port on the core instance is sized [8:0], where:

- qpll0refclksel\_in[2:0] connects to the transceiver common instance at location GTHE3\_COMMON\_X0Y2.

- qpll0refclksel\_in[5:3] connects to the transceiver common instance at location GTHE3 COMMON X0Y5.

• qpll0refclksel\_in[8:6] connects to the transceiver common instance at location GTHE3\_COMMON\_X1Y3.

By vectoring in this manner, the user interface of the core is compact and predictable. As a convenience, the example design also provides per-primitive signals that are assigned the relevant bit slices of the concatenated vectors. See Chapter 5, Example Design, for more details on example design features.

This document does not provide guidance on the usage of the transceiver primitive ports. See the *UltraScale Architecture GTH Transceivers User Guide* (UG576) [Ref 1] or *UltraScale Architecture GTY Transceivers User Guide* (UG578) [Ref 2] for relevant details.

Table 2-24: Transceiver Common Ports

| Name               | Direction | Width                                                                                                           | Description                                                                                                          |

|--------------------|-----------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| bgbypassb_in       | Input     | 1 × Num. commons                                                                                                | Connects to BGBYPASSB on transceiver common primitives                                                               |

| bgmonitorenb_in    | Input     | 1 × Num. commons                                                                                                | Connects to BGMONITORENB on transceiver common primitives                                                            |

| bgpdb_in           | Input     | 1 × Num. commons                                                                                                | Connects to BGPDB on transceiver common primitives                                                                   |

| bgrcalovrd_in      | Input     | 5 × Num. commons                                                                                                | Connects to BGRCALOVRD on transceiver common primitives                                                              |

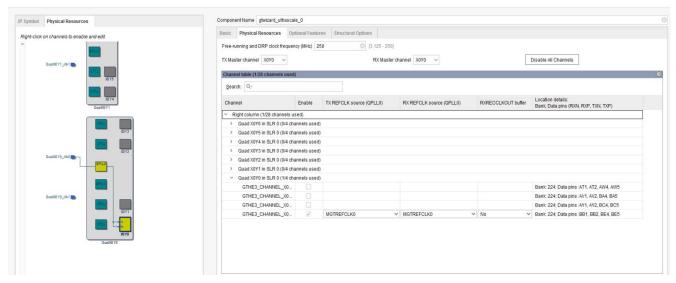

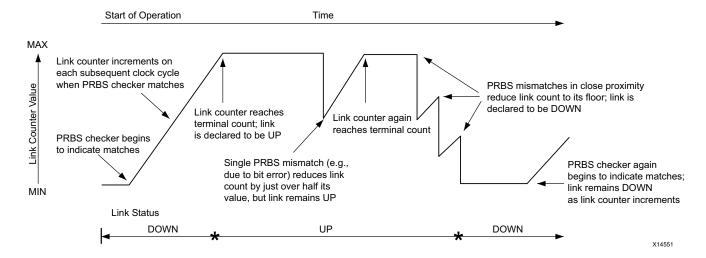

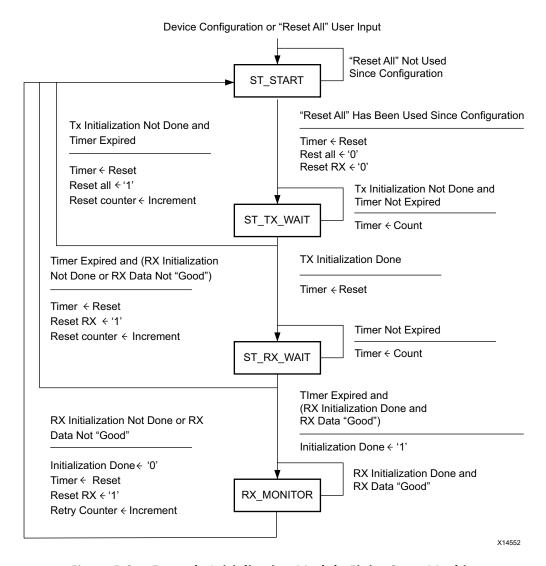

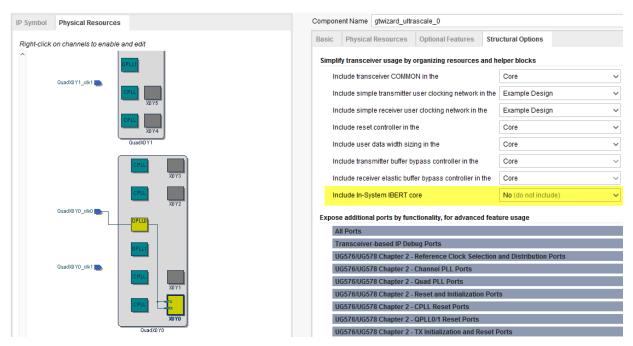

| bgrcalovrdenb_in   | Input     | 1 × Num. commons                                                                                                | Connects to BGRCALOVRDENB on transceiver common primitives                                                           |