# 低电压逻辑接口

### 简介

目前,对更快、更小、成本更低的产品的旺盛需求推动着降低电源电压这一革命性的发展趋势。在这种需求的推动下,硅尺寸从20世纪80年代初的2 µm减小到0.90 nm和45 nm,这种小尺寸的硅被广泛用于当今的最新FPGA、微处理器和DSP设计当中。随着器件尺寸的不断缩小,实现器件最佳性能的电压也降至了5 V以下。这体现在当今的FPGA、微处理器和DSP之中,其最佳内核工作电压最低达1 V或者更低。

对低电压DSP的强烈兴趣十分清楚地体现在了5 V和3.3 V器件的销量变化中。3.3 V DSP的销售增长速度达DSP市场中所有其他器件的两倍以上(所有DSP器件的销量增长速度为30%,3.3 V器件则超过了70%)。在大批量/高增长便携式市场对具有低电压DSP全部特性的信号处理器的需求保持高速增长的背景下,这一趋势将继续下去。

一方面,低电压IC的工作在低功耗模式下,有利于缩小芯片面积,提高速度。另一方面,低电压IC必须与其他IC连接,而这些IC却工作于更大的 $V_{DD}$ 电源电压,因而会导致接口兼容性问题。尽管更低的工作电压意味着更小的信号摆幅、更小的开关噪声,从而低电源电压IC的噪声裕量也更低。

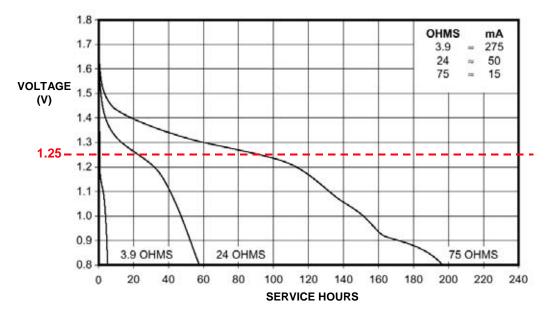

2.5 V器件之所以大行其道,其部分原因在于,它们支持2个AA碱性电池供电。图1展示了AA电池在各种负载条件下的典型放电特性(参考文献2)。请注意,在15 mA的负载电流下,电压可以维持在+1.25 V以上(两节电池串联则为2.5 V)近100小时。因此,可以在2.5 V±10%(2.25 V - 2.75 V)的电源电压下有效地进行低功耗工作的IC对于便携式设计十分有用。

Courtesy: Duracell, Inc., Berkshire Corporate Park, Bethel, CT 06801 http://www.duracell.com

图1: 金霸王MN1500 "AA"碱性电池的放电特性

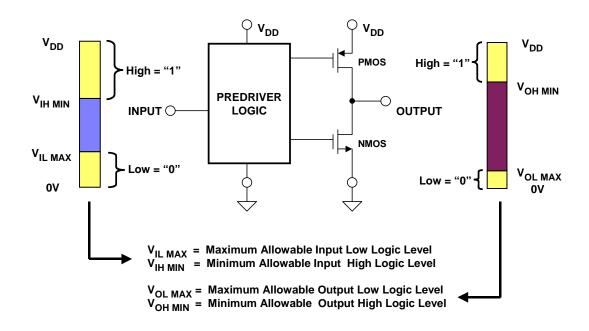

为了了解工作于不同 $V_{DD}$ 电源电压下的IC接口兼容性的问题,不妨先看看典型CMOS逻辑级的结构,如图2所示。

图2: 典型CMOS IC输出驱动器的配置

注意,输出驱动器级由一个PMOS和一个NMOS晶体管构成。当输出为高时,PMOS晶体管通过低导通电阻( $R_{ON}$ )把输出连接至+ $V_{DD}$ 电源,NMOS晶体管关闭。当输出为低时,NMOS晶体管通过导通电阻把输出连接至地,PMOS晶体管关闭。CMOS输出级的 $R_{ON}$ 在5  $\Omega$ 至50  $\Omega$ 之间不等,具体取决于晶体管的尺寸,而尺寸又决定着输出电流驱动能力。

典型逻辑IC的电源和地是分离于输出驱动器和电路其余部分之间的(包括前置驱动器)。这是为了维持干净的电源,以减少噪声和地反弹对I/O电平的影响。这一点越来越重要,因为在I/O驱动器规格中,尤其是在低电压下,增加容差和顺度是至关重要的。

图2同时展示了决定着产生有效高逻辑电平或低逻辑电平所需要的最低和最高输入和输出电压的"条形"。注意,对于CMOS逻辑来说,实际输出逻辑电平取决于晶体管的驱动电流和和RON。对于轻负载,输出逻辑电平非常接近0 V和+V<sub>DD</sub>。另一方面,输入逻辑阈值取决于IC的输入电路。

"输入"条中有三个部分。最下面的部分展示的是被理解为逻辑低电平的输入范围。对于5 V TTL,该范围在0 V和0.8 V之间。中间部分为被理解为既不是逻辑低电平也不是逻辑高电平的输入电压范围。最上面的部分展示的是被理解为逻辑高电平的输入范围。对于5 V TTL,该范围为2 V 至5 V。

类似地,"输出"条中也有三个部分。最下面的范围表示逻辑低电平输出的容许电压。对于 5 V TTL, IC必须输出0 V至0.4 V的电压。中间部分所示电压范围不是有效的高电平或低电平——除非在电平之间过渡时,否则器件不得发送处于该部分的电平。最上面的范围表示逻辑高电平输出信号的容许电压范围。对于5 V TTL,该电压在2.4 V和5 V之间。图表中并未反映逻辑标准输入允许的10%过冲/下冲容差。

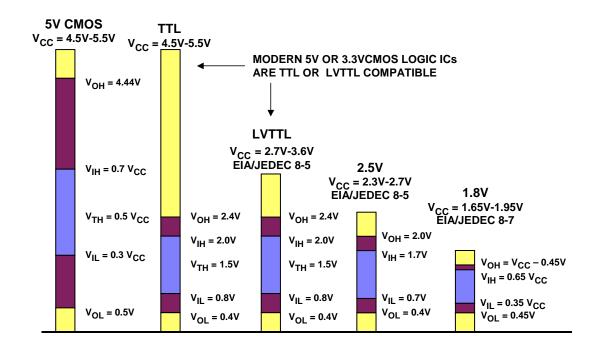

图3总结了基于这些定义的现有逻辑标准。注意,经典CMOS逻辑(如4000系列)的输入阈值 定义为0.3  $V_{DD}$ 和0.7  $V_{DD}$ 。然而,目前使用的多数CMOS逻辑电路兼容TTL和LVTTL电平,它们是目前DSP的主流5 V和3.3 V工作电压标准。注意,5 V TTL和3.3 V LVTTL输入和输出 阈值电压是相同的。其差异体现在容许高电平的上限方面。

图3: 标准逻辑电平

国际标准组织JEDEC(联合电子设备工程委员会)制定了2.5 V标准(JEDEC 8-5号标准)和1.8 V标准(参考文献3)。还有众多其他低电压标准,比如GTL(射补收发器逻辑)、BTL(基架收发器逻辑)、ECL(射极耦合逻辑)、PECL(正ECL逻辑)和LVDS。然而,多数这些标准都是针对具体的应用市场,并非针对通用半导体系统。

从图3可以看出,对连接两个工作于不同标准的IC时可能存在的问题进行可视化是有可能的。一个例子是把一个5 V TTL器件连接至一个3.3 V LVTTL IC。5 V TTL高电平超过了LVTTL的处理能力(>3.3 V)。这可能给LVTTL芯片造成永久性损坏。另一个可能的问题是在系统中用2.5 V IC驱动5 V CMOS器件。来自2.5 V器件的逻辑高电平不足以达到5 V CMOS输入的逻辑高电平的条件(V<sub>IH MIN</sub> = 3.5 V)。这些例子展示了两类潜在的逻辑电平兼容性问题——要么是用过高的电压驱动器件,要么驱动电压过低,达不到接收IC端的有效逻辑高电平的要求。这些接口问题带来了两个重要的概念:电压容差和电压顺度。

## 电压容差和电压顺度

电压容差型器件的I/O引脚可以承受大于其 $V_{DD}$ 的电压。例如,如果一个器件的 $V_{DD}$ 为 2.5 V,可以接受等于3.3 V的输入电压,并且其输出端可以承受3.3 V的电压,则称该2.5 V 器件的容差电压为3.3 V。输入电压容差的意义是显而易见的,但输出电压容差却需要稍加说明。在高电平状态下,2.5 V CMOS驱动器输出的表现类似于连接至2.5 V电压的小电阻 (PMOS FET的 $R_{ON}$ )。显然,把该器件的输出直接连接到3.3 V的电压,过高的电流很可能会

损坏器件。然而,如果2.5 V器件有一个三态输出,连接着一个同样由3.3 V IC驱动的总线,则其意义将更加明显。即使2.5 V IC处于关闭(第三态)条件,3.3 V IC也可驱动高于2.5 V的总线电压,结果可能损坏2.5 V IC输出。

电压顺从型器件可以接收来自工作电压大于其自身 $V_{DD}$ 的器件的信号,也可把信号发送到此类器件。例如,如果一个器件的 $V_{DD}$ 为2.5 V,并可向3.3 V器件发送信号或者从其接收信号,则称该2.5器件的顺从电压为3.3 V。

5 V CMOS与3.3 V LVTTL器件之间的接口展现了电压容差的缺乏; LVTTL IC输入由5 V CMOS 器件输出过驱。2.5 V JEDEC与5 V CMOS器件之间的接口展示了电压顺度的缺乏; EDEC IC 的高输出电平不符合5 V CMOS器件的输入电平要求。

### 利用NMOS FET"总线开关"连接5V系统和3.3V系统

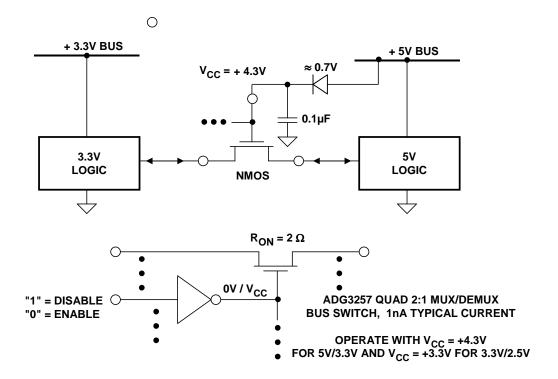

在连接工作于不同电压标准的IC时,我们往往被迫添加额外的分离式元件,以确保电压容差和电压顺度。例如,为了在5 V和3.3 V逻辑之间实现电压容差,可以使用ADG3257一类的总线开关电压转换器(另见参考文献4和5)。总线开关将限制应用于IC的电压。这是为了避免应用大于接受器件容许范围的高输入电压。

举例来说,可以在5 V CMOS和3.3 V LVTTL IC之间放置一个总线开关,此时,这两种器件就可以正常发送数据了,如图4所示。基本而言,总线开关是一种NMOS FET。如果将4.3 V 的电压置于FET的栅极上,则最大可通过信号为3.3 V(比栅极电压约低1 V)。如果输入和输出均低于3.3 V,则NMOS FET将充当低电阻( $R_{ON}\approx 2~\Omega$ )。随着输入接近3.3 V,FET导通电阻会增大,从而限制信号输出。ADG3257是一款四通道2:1 Mux/Demux总线开关,具有一个栅极驱动使能引脚,如图4下半部分所示。ADG3257的 $V_{CC}$ 设置栅极驱动的高电平。

图4: 采用NMOS FET的+5 V/+3.3 V 双向接口实现电压容差

在5 V/3.3 V系统板上实现4.3 V电源电压的一种方式是在5 V电源和总线开关 $V_{cc}$ 之间放置一个硅二极管,如图4所示。对于3.3 V/2.5 V应用, $V_{cc}$ 引脚可以直接连接至+3.3 V电源。有些总线开关设计用于直接工作于3.3 V或5 V的电源电压,并在内部产生内部栅极偏置电平。

在这种混合型逻辑设计中,总线开关可以消除电压容差问题。总线开关有一个便利的特性,即它们是双向的;借助该特性,设计人员可以在两个IC之间放一个总线转换器,而无需为输入和输出信号创建额外的路由逻辑。

总线开关会增加总功耗以及系统布局所需要的总面积。由于电压总线开关通常为CMOS电路,因此,其额定功耗都很低。连续功耗增加部分的平均值为每个封装5 mW(10个开关),这与通过电路的信号频率无关。总线开关每个封装一般有8到20个I/O引脚,大约占用25至50 mm²的电路板空间。

在电路中增加接口逻辑的一个顾虑是可能导致传播延迟增加。增加传播延迟可能给设计带来诸多时序问题。总线开关的传播延迟值非常低。

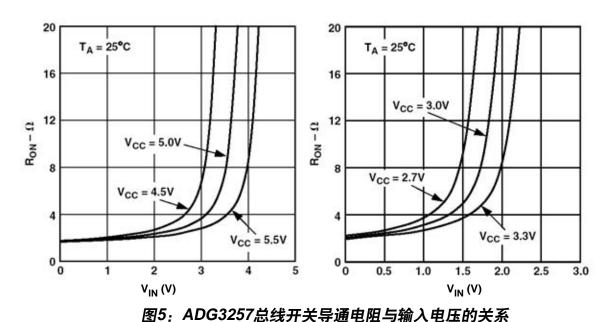

实际上,总线开关不会增加传播延迟(ADG3257的典型值为0.1 ns),只会增加在由理想电压源驱动时的开关的典型 $R_{ON}$ 以及负载电容的RC延迟。由于时间常数一般比典型驱动信号的上升/下降时间要小得多,所以总线开关只会为系统增加极小的传播延迟。因此,低 $R_{ON}$ 是总线开关的关键特性,因为开关导通电阻和总线电容会形成一个单极滤波器,结果会增加延迟、降低最大数据速率。ADG3257的典型导通电容为10 pF,再加上4  $\Omega$ 的 $R_{ON}$ ,结果会产生约90 ps的上升/下降时间。图5所示为ADG3257的导通电阻和5.5、5、4.5、3.3、3.0以及2.7 V电源输入电压的函数关系。作为输入电压函数的最大导通电压如图6所示。

T<sub>A</sub> = 25°C TA = 25°C  $V_{CC} = 3.6V$  $V_{CC} = 5.5V$ 3 OUTPUT VOLTAGE - V OUTPUT VOLTAGE - V  $V_{CC} = 5.0V$  $V_{CC} = 3.3V$  $V_{CC} = 4.5V$ 2 V<sub>CC</sub> = 3.0V 0.5 1 2 5 0 1.0 1.5 2.0 2.5 3.0 3.5 INPUT VOLTAGE - V INPUT VOLTAGE - V

图6: ADG3257总线开关最大导通电压与输入电压的关系

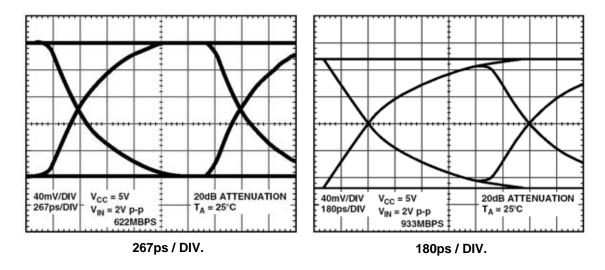

ADG3257在622 Mbps和933 Mbps工作频率下的眼图如图7所示。

图7: 622 Mbps和933 Mbps数据速率下的眼图

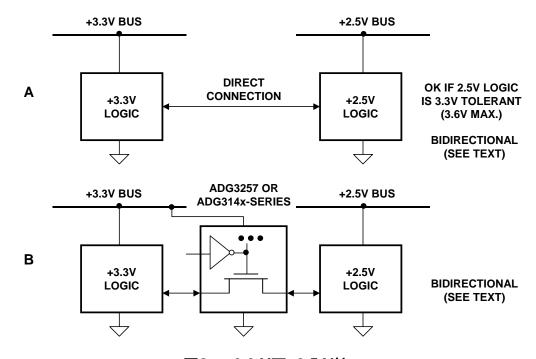

#### 3.3V/2.5V接口

图8展示了3.3 V至2.5 V逻辑接口的两种可能性。上部图示(A)展示的是直接连接模式。只要 2.5 V IC输入端的容差电压为3.3 V,则该模式有效。如果2.5 V IC不能承受3.3 V,则可使用 ADG3231一类的低电压总线开关。在多数情况下,3.3 V和2.5 V两种系统之间的连接可以是 双向的,即使2.5 V逻辑 $V_{\rm CH}$ 的额定值与3.3 V逻辑的 $V_{\rm H}$ 额定值都是+2.0 V(参见前面的图3)。 这一点需要进一步的讨论。

图8: +3.3 V至+2.5 V接口

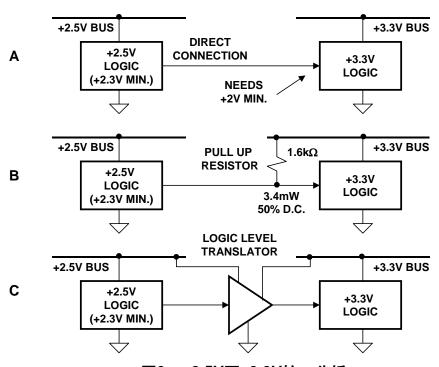

图9A所示为2.5 V和3.3 V逻辑之间的直接连接。为了使该连接有效,据JEDEC规范, 2.5 V输出的最小值不得低于2 V。当2.5 V输出端无负载时, 3.3 V IC输入通过PMOS晶体管驱动器的导通电阻直接连接至+2.5 V。这为2.5 V的额定电源电压提供了0.5 V的噪声裕量。然而, 2.5 V总线的容差允许其下降至2.3 V的最小值,此时,噪声裕量降至0.3 V。这在相对安静的环境中可能仍然有效,但是,如果电源电压存在噪声,则可能有些牵强。

如图9B所示,增加一个1.6 kΩ上拉电阻,在3.3 V器件输入电流的作用下,可以确保2.5 V输出不会降至2.5 V以下,但2.3 V电源的噪声裕量下降问题仍然存在。在50%的占空比下,电阻给每个输出端增加约3.4 mW的功耗。

图9C展示了2.5 V和3.3 V逻辑之间更可靠的一种接口,其中使用了ADG3231一类的逻辑转换器。这就解决了(A)和(B)两种情况下的全部噪声裕量问题,每个输出端只需大约2 μA(最大值)的功耗。

图9: +2.5V至+3.3V接口分析

#### 3.3V/2.5V、3.3V/1.8V、2.5V/1.8V接口

ADG3241、ADG3242、ADG3243、ADG3245、ADG3246、ADG3247、ADG3248和 ADG3249是针对3.3 V或2.5 V电源而优化过的低电压总线开关。该系列包括1位、2位、8位、10 位和双通道8位开关,全部都是双端口开关。ADG3241、ADG3242、ADG3245、ADG3246、ADG3247和ADG3249具有2.5 V或1.8 V可选电平转换能力。该系列为3.3 /2.5 V、

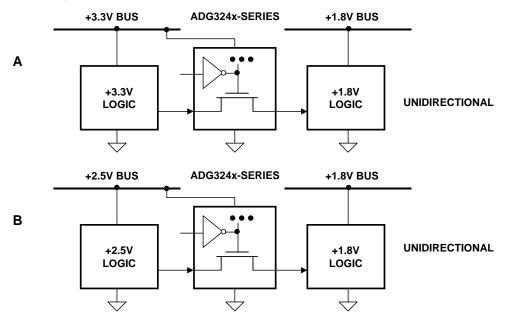

3.3 /1.8 V和2.5 /1.8 V单向接口提供了一种快速的低功耗解决方案。图10所示ADG32xx系列分别用作3.3 /1.8 V电平转换器和2.5 /1.8 V转换器。

图10: +3.3 V至+1.8 V、2.5 V至+1.8 V单向接口

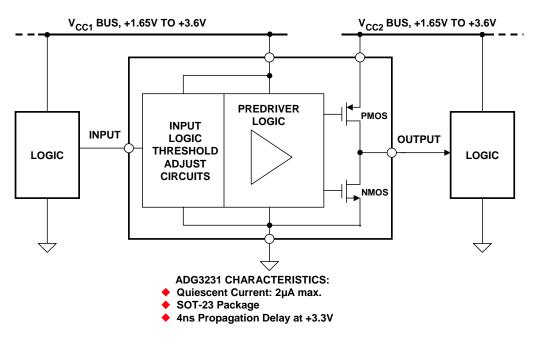

从1.8 V转换至2.5 V,从1.8 V转换至3.3 V(如前所述,有时是从2.5 V转换至3.3 V)要求使用类似于图11所示ADG3231一类的逻辑转换器。两个电压总线的值可以为1.65 V和3.6 V之间的任意值。ADG3231是一款采用SOT-23封装的单通道转换器,ADG3232是一款同样采用SOT-23封装的2:1多路复用器/电平转换器。

图11: ADG3231低电压逻辑电平转换器

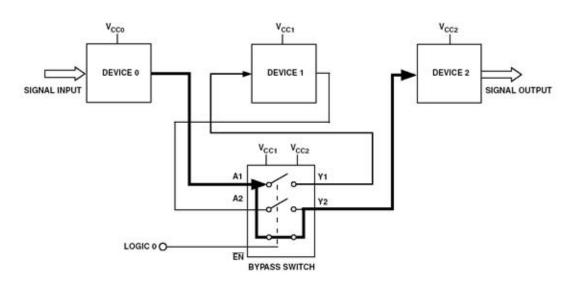

ADG3233是一款采用亚微米工艺设计的旁路开关,可支持最低1.65 V的工作电压。该器件可以保证在1.65 V至3.6 V的电源电压范围内正常工作,采用双电源电压,支持双向电平转换,也就是将低电压转换为高电压,反之亦然。信号路径是单向的,也就是说数据只能从A流向Y。这类器件可以用于要求旁路功能的应用之中。非常适合JTAG链中或者菊花链环路中的旁路器件。一个开关可以用于一个器件或多个器件,从而轻松旁路链中的一个或多个器件。这在测试JTAG链或菊花链应用中的器件时特别有用,用户不必更改特定器件的设置,从而节省时间开销。

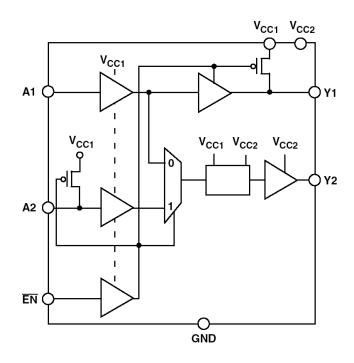

这款旁路开关采用所需引脚数量的两种最小封装。8引脚SOT-23封装仅需8.26 mm×8.26 mm 电路板空间,而MSOP封装则占用大约15 mm×15 mm电路板面积。图12所示为ADG3233的功能框图。

图12: ADG3233低电压1.65 V至3.6 V 逻辑电平转换器和旁路开关

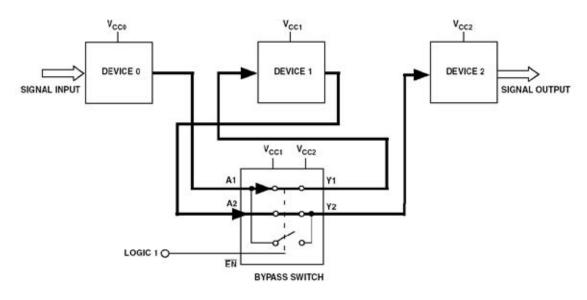

图13所示旁路开关用于正常模式。在该模式下,信号路径是从A1到Y1及从A2到Y2。该器件将把应用到A1的信号的电平转换为一种 $V_{\rm CCl}$ 逻辑电平(这种电平转换可以针对高电平电源,也可针对低电平电源),并把信号路由至Y1输出,该输出在 $V_{\rm CCl}$ 电源下为标准 $V_{\rm Ol}/V_{\rm OH}$ 电平。然后,信号通过器件1,再回到旁路开关A2输入引脚。A2的逻辑电平输入是针对 $V_{\rm CCl}$ 电源而言的。信号的电平将从 $V_{\rm CCl}$ 转换至 $V_{\rm CCl}$ ,并路由到旁路开关的Y2输出引脚。Y2输出逻辑电平是针对 $V_{\rm CCl}$ 电源而言的。

图14展示的是用在旁路操作中的器件。现在的信号路径是从A1直接到Y2,从而完全绕过了器件1。信号的电平将转换至一种 $V_{\rm CC2}$ 逻辑电平,并提供给Y2,在这里,信号可以直接应用至器件2的输入引脚。在旁路模式下,Y1上拉至 $V_{\rm CC1}$ 。图13和图14中的三种电源可以是任意电源组合,即 $V_{\rm CC0}$ 、 $V_{\rm CC1}$ 和 $V_{\rm CC2}$ 可以是任意电源组合,如1.8 V、2.5 V和3.3 V。

图13: 正常模式下的ADG3233旁路开关

图14: 旁路模式下的ADG3233旁路开关

## 内部形成的电压容差和电压顺度

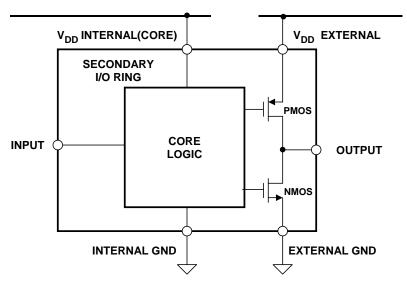

现代高性能CMOS DSP和微处理器一般采用1 V至2 V的内核电压。这种低电压会带来最佳的速度-功耗性能。然而,内核中的逻辑电平并不兼容标准的2.5 V或3.3 V I/O接口。这个问题一般以图15所示方式解决,其中,逻辑内核以低电压工作,但输出驱动器则以2.5 V或3.3 V 标准电源电压工作。

$V_{DD}$  EXTERNAL = +2.5V OR +3.3V  $V_{DD}$  CORE = +0.9V TO +1.8V (DEPENDING ON PROCESSOR) INPUT +2.5V or +3.3V TOLERANT

图15: 具有次级I/O环的CMOS IC的内部顺度和容差

许多IC制造商采取的技术是提供一个次级I/O环,即I/O驱动器由2.5 V或3.3 V电源驱动,因此,这种器件可以兼容2.5 V或3.3 V逻辑电平。注意,输入必须能顺从并承受I/O电源电压。在这种双电源逻辑IC的设计中,需要考虑多种问题:

- 上电时序控制:如果需要用两个电源来提供额外的IC容差/顺度,那么该上电时序是什么?是要求电源同时开启,还是要求器件只在内核上或仅在I/O环上提供电压?如果内核电压是用低压差线性调节器从I/O电源电压产生的,则可以很容易地解决这个问题。时序控制电路也可用来解决这些问题。

- 工艺支持和静电放电(ESD)保护:以IC制造工艺生产的晶体管必须能承受并驱动高电压。高电压晶体管会形成额外的制造成本,因为它们需要更多的处理步骤以形成高电压容差。采用标准晶体管的设计需要额外的电路。I/O驱动器也必须为器件提供ESD保护。多数电流设计把过压限制为超过电源电压的一个二极管压降(0.7 V)以下。更大的过压保护要求采用更多的串联二极管。

- 内部高电压的产生: PMOS晶体管需要置于一个基板阱中,后者与最高的片上电压相关联,以避免横向二极管开启、消耗过多的电流。该高电压既可以用电荷泵在片上产生,也可用外部电源产生。这种要求可能使设计复杂化,因为我们无法有效利用电荷泵来产生较高的电压,并同时实现低待机电流。多数情况下,该电压以外部方式提供。

- 芯片面积: 芯片尺寸是降低成本、提高产量的一个主要因素。容差电路和顺从电路可能要求更多或更大的I/O器件来实现目标性能水平。

- 测试:由于内核和I/O可以在不同电压下工作,因此,测试器件在各种可能电压组合下的特性是非常复杂的,会增加IC的总体成本。

### 参考文献

- 1. P. Alfke, "Low-Voltage FPGAs Allow 3.3V/5V System Design," *Electronic Design*, p. 70-76, August 18, 1997.

- 2. AA Alkaline Battery Discharge Characteristics, Duracell Inc., Berkshire Corporate Park, Bethel, CT 06801, www.duracell.com.

- 3. Joint Electron Device Engineering Council (JEDEC), <a href="www.jedec.org">www.jedec.org</a>, Standard JESD8-5, October 1995, and Standard JESD8-7, February, 1997,

- 4. QS3384 Data Sheet, Integrated Device Technology (IDT), Inc., 2975 Stender Way, Santa Clara, CA 95054, www.idt.com

- 5. Pericom Semiconductor Corporation, 2380 Bering Drive, San Jose, CA 95131, http://www.pericom.com

- 6. H. Johnson, M. Graham, High Speed Digital Design, Prentice Hall, 1993.

- 7. Eva Murphy and Catherine Redmond, "Bus Switches for Speed, Safety, and Efficiency: What They Are and What You Should Know about Them," *Analog Dialogue* 36-06, Analog Devices, Inc., 2002.

- 8. Hank Zumbahlen, *Basic Linear Design*, Analog Devices, 2006, ISBN: 0-915550-28-1. Also available as *Linear Circuit Design Handbook*, Elsevier-Newnes, 2008, ISBN-10: 0750687037, ISBN-13: 978-0750687034. Chapter 12

- 9. Walt Kester, <u>Analog-Digital Conversion</u>, Analog Devices, 2004, ISBN 0-916550-27-3, Chapter 9. Also available as *The Data Conversion Handbook*, Elsevier/Newnes, 2005, ISBN 0-7506-7841-0, Chapter 9.

Copyright 2009, Analog Devices, Inc. All rights reserved. Analog Devices assumes no responsibility for customer product design or the use or application of customers' products or for any infringements of patents or rights of others which may result from Analog Devices assistance. All trademarks and logos are property of their respective holders. Information furnished by Analog Devices applications and development tools engineers is believed to be accurate and reliable, however no responsibility is assumed by Analog Devices regarding technical accuracy and topicality of the content provided in Analog Devices Tutorials.