## 运算放大器输入失调电压

### 输入失调电压定义

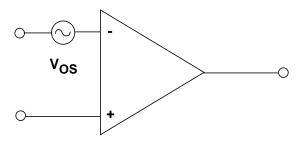

理想状态下,如果运算放大器的两个输入端电压完全相同,输出应为0 V。实际上,还必须在输入端施加小差分电压,强制输出达到0。该电压称为输入失调电压 $V_{os}$ 。输入失调电压可以看成是电压源 $V_{os}$ ,与运算放大器的反相输入端串联,如图1所示。

- Offset Voltage: The differential voltage which must be applied to the input of an op amp to produce zero output.

- Ranges:

Chopper Stabilized Op Amps: <1μV</li>

General Purpose Precision Op Amps: 50-500μV

Best Bipolar Op Amps: 10-25μV

Best JFET Input Op Amps: 100-1,000μV

High Speed Op Amps: 100-2,000μV

Untrimmed CMOS Op Amps: 5,000-50,000μV

DigiTrim™ CMOS Op Amps: <100μV-1,000μV</li>

#### 图1: 典型的运算放大器输入失调电压

斩波稳定型(也称自稳零)运算放大器的 $V_{os}$ 小于1 μV(如<u>AD8538</u>、<u>AD8551</u>、<u>AD8571</u>、<u>AD8628</u>、 <u>AD8630</u>),最好的精密双极性运算放大器(super-beta或偏置稳定型)的最大失调电压可低至 25 μV(<u>OP177F</u>)。最好的调整后JFET输入型运算放大器的失调电压约为100 μV(<u>AD8610B</u>、 <u>AD8620B</u>),未调整的CMOS运算放大器则为5至50 mV。

但是, ADI DigiTrim<sup>™</sup> CMOS运算放大器的失调电压小于100 μV(如<u>AD8603</u>、<u>AD8607</u>、 <u>AD8609</u>、<u>AD8605</u>、<u>AD8606</u>、<u>AD8608</u>)。"精密"运算放大器的V<sub>os</sub>一般小于0.5 mV, 某些高速放大器可能略差一些。本教程稍后将介绍DigiTrim技术。

### 输入失调电压漂移与老化效应

输入失调电压随温度变化,其温度系数称为 $TCV_{os}$ ,更常见的说法是温漂。失调温漂受运算放大器失调调整的影响,但是当双极性输入运算放大器的失调电压降至最低后,温漂可能会低至 $0.1~\mu V/^{\circ}C(OP177F)$ 的典型值)。对一系列通用精密运算放大器而言,更典型的温漂值范围为1至 $10~\mu V/^{\circ}C$ 。大多数运算放大器都有 $TCV_{os}$ 额定值,但是某些却有第二个最大 $V_{os}$ 值,并保证在工作温度范围内实现。这样的指标用处不大,因为无法保证 $TCV_{os}$ 稳定不变或具有单调性。

失调电压还会随时间变化,也称老化。老化通常以 $\mu$ V/月或 $\mu$ V/1000小时来表示,但是可能会有问题。由于老化是一个"醉汉走路"现象,与经过时间的平方根成比例。因此,1  $\mu$ V/1000小时的老化率就会变成大约3  $\mu$ V/年(而不是9  $\mu$ V/年)。

OP177F的长期稳定性约为0.3 μV/月。这是指首次工作30天后的一段时间。除去刚开始工作的一小时,这些器件在最初工作30天内的失调电压变化通常小于2 μV。

由于自稳零电路会消除所有因老化产生的失调,因此斩波稳定运算放大器的长期稳定性并没有明确规定。

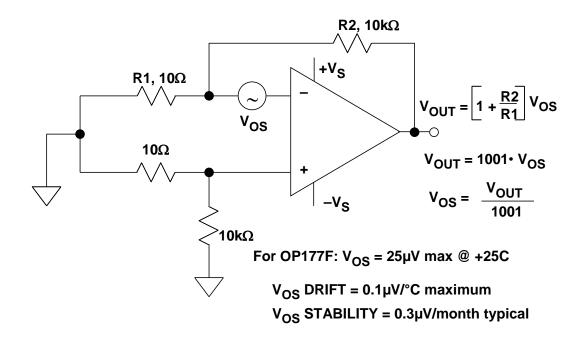

## 测量输入失调电压

测量几微伏的输入失调电压时,测试电路产生的误差不应比失调电压本身更多。图2所示为测量失调电压的标准电路。该电路以1001的噪声增益放大输入失调电压,测量采用精确数字电压表在放大器输出端完成。折合到输入端(RTI)的失调电压通过输出电压除以噪声增益计算得出。从输入端获得源阻抗较小,因而产生的偏置电流对测量的失调电压的影响可忽略不计。例如,流经10 Ω电阻的2 nA偏置电流产生的折合到输入端误差为0.02 μV。

图2: 测量输入失调电压

该电路很简单,测试精密运算放大器时,除非小心注意,否则结果会不准确。可能存在的最大误差源来自寄生热电偶结点,这是在两种不同金属连接的时候形成的。该热电偶电压范围可达2 μV/℃至40 μV/℃以上。注意,该电路的同相输入端额外增加了"伪"电阻,目的是精确匹配/平衡反相输入路径中的热电偶结点。

测量精度还取决于元件的机械布局,确切地说,元件在PC板上的位置。记住,电阻等器件的两个连接点会产生两个大小相等、极性相反的热电电压(假定连接至相同金属,例如PC板上的铜走线)。这两个电压会相互抵消,前提是假定两者温度完全相同。连接点整洁和引线长度较短都能够尽可能减小温度梯度,提高测量精度。

应尽可能减小测试电路中的气流,这样所有的热电偶结点就能稳定在同一温度。有些情况下,电路应安放在小型封闭容器中,以消除外部气流的影响。电路应水平放置在某个表面,这样气流就会向上对流,流出电路板顶部,而不是像电路板垂直安放时那样流经元件。

测量整个温度范围的失调电压温漂是一项更加艰巨的挑战。将含有受测放大器的印刷电路板放在采用泡沫隔离的小盒子或塑料袋中,这样就可以防止恒温室气流导致寄生热电偶产生温度梯度。如果需要进行冷测试,建议采用干式氮吹。另一种方法是用Thermostream加热器/冷却器对放大器本身采取局部温度循环,但是,这些器件可能会产生相当大的气流,带来麻烦。图2的测试电路通常适用于很多放大器。采用绝对值低的小电阻(如10  $\Omega$ )可以尽量减小偏置电流产生的误差。

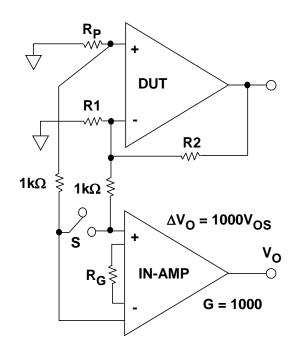

图3所示是另一种 $V_{os}$ 测量方法,适合偏置电流较高和/或不相等的情况(如采用电流反馈运算放大器时)。在这种测量方法中,一个仪表放大器通过隔离电阻连接至运算放大器输入端,并为测量提供增益。然后,仪表放大器的失调电压(采用S闭环测量)必须从最终的 $V_{os}$ 测量值中减去。

图3: 采用仪表放大器的另一种输入失调电压测量方法

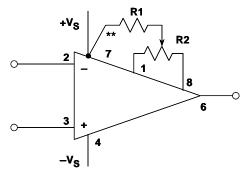

# 采用"零点校准"引脚调整失调电压

许多单路运算放大器都有供可选失调零点校准使用的引脚。为了使用这项功能,两个引脚应通过电位计连接,游标通过电阻移动到其中一个电源,通常如图4所示。注意,如果游标不慎连接到错误的电源,运算放大器很可能会受损,更换运算放大器类型时,这个问题很常见。运算放大器若设计周全,其失调调整范围不会超过最低等级器件最大V<sub>os</sub>的两至三倍,从而尽可能降低敏感度。然而,运算放大器失调调整引脚的电压增益实际上可能大于其信号输入端的增益!因此,必须保持这些引脚无噪声。注意,千万不要采用长引线将运算放大器连接至相距较远的零值电位计。

- ◆ \*\* Wiper connection may be to either +V<sub>S</sub> or -V<sub>S</sub> depending on op amp

- R values depend on op amp. Consult data sheet

- Use to null out input offset voltage, not system offsets!

- ♦ There may be high gain from offset pins to output Keep them quiet!

- Nulling offset causes increase in offset temperature coefficient, approximately 4µV/°C for 1mV offset null for FET inputs

#### 图4: 失调调整引脚

如上所述,运算放大器随温度产生的失调温漂会根据其失调调整设置发生变化。因此,应当只采用内部调整引脚来调整运算放大器自身的失调,不校正任何系统失调误差,因为这样做会导致温度漂移上升。对每毫伏零点校准失调电压而言,FET输入运算放大器的漂移影响约为4 μV/°C。一般而言,最好选择合适的器件/等级来控制失调电压。

## 失调调整(外部方法)

如果运算放大器没有失调调整引脚(常见的双路运放和所有的四路运放都没有),但仍然需要调整放大器和系统失调,就可以采用外部方法。如果利用系统可编程电压完成失调调整,这种方法同样也最有效,例如用DAC。

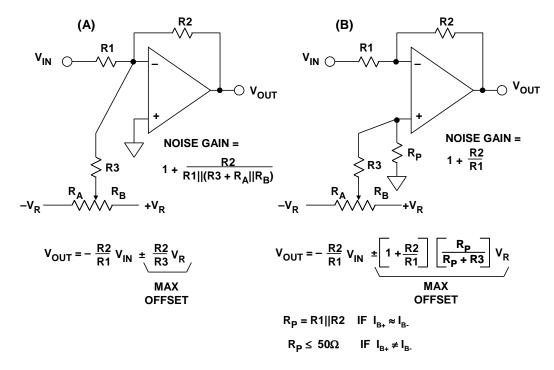

采用反相运算放大器配置时,向反相输入注入电流是最简单的方法,如图5A所示。这种方法的缺点是由于R3和电位计电阻采用并行路径,噪声增益可能会有所上升。要减少由此增加的噪声增益,可将 $\pm V_R$ 设置得足够大,这样R3的值就会远大于R1 $\parallel$ R2。注意,如果电源稳定且无噪声,就可以用作 $\pm V_R$ 。

图5B显示如何通过向同相输入注入小失调电压来调整失调。该电路优于图5A的电路,因为不会增加噪声增益(但是需要增加 $R_p$ )。如果运算放大器与输入偏置电流匹配, $R_p$ 应等于 R1|| R2(以尽量减小增加的失调电压)。否则,RP应小于50  $\Omega$ 。如果值较高,建议在高频时 将 $R_p$ 进行旁路分流。

图5: 反相运算放大器外部失调调整方法

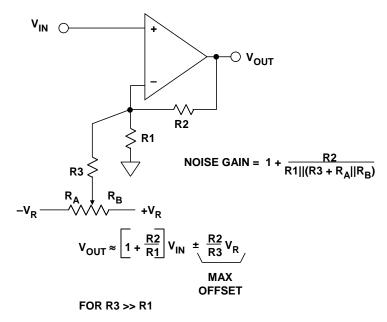

在同相模式中使用运算放大器时,可利用图6所示的电路注入小失调电压。该电路在失调较小时效果较好,其中R3可设置为远大于R1。否则就要注意,由于调整了失调电位计,信号增益可能会受到影响。但是,如果R3连接至固定的低阻抗基准电压源  $\pm V_R$ ,增益就能保持稳定。

图6: 同相运算放大器外部失调调整方法

## 失调电压调整过程

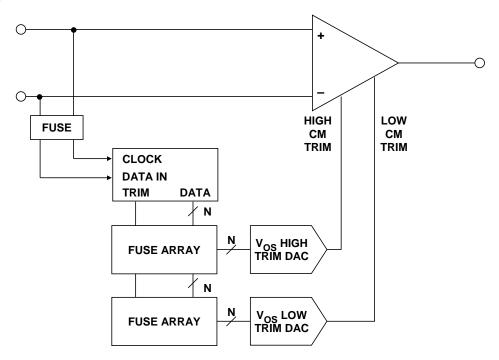

DigiTrim™ CMOS运算放大器系列利用数字技术的优势,目的是尽量减小通常与CMOS放大器有关的失调电压。失调电压调整在器件封装好之后完成。数字码输入器件中,根据器件等级将失调电压调整至1 mV以下。不需要进行晶圆测试,ADI公司的专利技术DigiTrim™也不需要额外的引脚来实现该功能。这些器件具有轨到轨输入和输出,NMOS和PMOS并行输入级采用DigiTrim单独进行调整,以尽量减小两对输入输出中的失调电压。图7所示为典型DigiTrim CMOS运算放大器的功能框图。

图7: ADI公司用于调整CMOS运算放大器的DigiTrim™技术

DigiTrim通过对数字加权电流源进行编程来调整失调电压。调整信息以特殊的数字序列通过现有的引脚输入。调整值可以暂时先编程、评估,然后经重新调整以实现最佳精度,最后再进行永久调整。调整完成后,调整电路就会闭锁,防止最终用户意外重新调整。

通过熔断晶硅熔丝实现物理调整是一种很可靠的方法,不需要额外的焊盘或引脚,也不需要特殊的测试设备。调整可以在封装后进行,这样就可以消除装配相关漂移。由于芯片产量较高,所以不需要进行晶圆级测试。

第一批采用该新技术的器件是ADI公司的AD8601、AD8602、AD8604(单路、双路、四路) 轨到轨CMOS放大器。高低共模情况下都要进行失调调整,从而使失调电压在整个共模输入电压范围内都小于500 μV。运算放大器的带宽为8 MHz,压摆率为5 V/μs,每个放大器的电源电流仅为640 μA。

AD8603、AD8605、AD8607(单路、双路、四路)系列的最大失调电压在整个共模范围内为 50 μV。增益带宽为400 kHz,每个放大器的电源电流仅为50 μA。

现在,有必要回顾一下其他常见的调整方法。ADI公司率先在精密放大器、基准电压源、数据转换器和其他线性IC上采用薄膜电阻和激光晶圆调整技术。通过调整,可以实现高达16位的精度,由于薄膜电阻本身具有极佳的温度稳定性,即使不用作调整,也可以增加器件的热稳定性和精度。薄膜沉积和图案成形过程都必须严格控制。激光调整系统也非常昂贵。因为无法进行封装内调整,所以装配相关温漂不易补偿。然而,在需要高精度和稳定性的精密集成电路中,晶圆级薄膜调整可以提供连续的高调整分辨率。

齐纳击穿通过电压使晶体管基极-发射极结点上的金属短路,从而移除某个电路元件。基极-发射极结点通常称为齐纳,但其机制实际上是结点的雪崩击穿。在基极-发射极结点的雪崩击穿过程中,极高的电流密度和局部发热会引起基极和发射极结点之间产生快速金属迁移,导致结点出现金属短路。通过适当的偏置(电流、电压和时间),短路的电阻值可以变得很低。如果将一系列这样的基极-发射极结点与电阻串并联,击穿选择的结点会使部分电阻串短路,从而调整总电阻值。

封装好的IC中可以进行齐纳击穿调整,以补偿装配相关的失调电压温漂。但是,封装内调整需要额外的封装引脚。另一种晶圆级调整则需要额外的探测点。由于工艺特征减少,探测点不能有效进行调整。因此,调整所需的芯片面积相对稳定,不受工艺尺寸的影响。调整结构中需要某些双极性晶体管,因此,完全基于MOS的工艺可能不具备齐纳击穿能力。这些调整属于分立式调整,因为每次击穿都会减去预定的电阻值。增加调整分辨率需要额外的晶体管和焊盘或引脚,这会大大增加总芯片面积和/或封装成本。该技术对大尺寸工艺而言性价比最高,这种工艺中调整结构和探测点占总芯片面积的比例相对较小。

1975年,在制定OP07行业标准的过程中,Precision Monolithics公司率先使用了齐纳击穿调整技术。OP07和其它类似器件必须能够采用±15 V以上的电源工作。因此,他们采用相对较大的器件尺寸,以满足高压要求,并且额外的探测点也不会明显增加芯片面积。

联接调整(link trimming)是指采用金属切割或多晶硅联接来去除某个连接。联接调整采用激光或高电流破坏并联电阻元件上的"短路"连接。去除连接可以增加组合元件的有效电阻。激光切割与薄膜激光调整的工作方式类似。激光束的局部高温导致材料发生变化,形成一个不导电区域,从而有效切割金属或导电晶硅连接器。

高电流联接调整法与齐纳击穿的作用相反,前者破坏导电连接,后者则形成导电连接。

联接调整结构往往比激光调整电阻结构更紧凑,通常不需要特殊工艺,但是采用激光切割时,可能必须根据激光的特点定制工艺。采用高电流调整法时,如果芯片产量较高,可能不需要晶圆级测试。激光切割法不需要额外的接触点,但是调整结构不会随着工艺特征尺寸而调整。激光切割联接不能在封装内完成,而且芯片上要有额外的探测点。此外,它还需要有额外的封装引脚进行封装内高电流调整。和齐纳击穿一样,联接调整也是分立式的。分辨率的提高需要额外的结构,会增加面积和成本。

EEPROM调整采用特殊的非易失性数字存储器来存储调整数据。存储的数据位通过片上 DAC控制调整电流。

存储器电池和DAC随工艺特征尺寸调整。封装内调整和客户系统内调整都可以实现,从而可以调整消除装配相关漂移。如果芯片产量合适,就不需要进行晶圆级测试。对正常混合信号测试器系统以外进行测试不需要特殊硬件,不过开发测试软件可能比较复杂。

由于调整可以覆写,有可能会定期对系统重新编程,以处理长期漂移,或根据新的要求修改系统特性。重新编程的周期数量可能由工艺决定,而且是有限的。大多数EEPROM工艺都提供足够的覆写周期,以便进行常规重新校准程序。

这种调整方法不需要特殊处理。存储的调整数据在某些情况下可能会丢失,尤其是在工作 温度较高时。至少需要一个额外的数字接触点/封装引脚将调整数据输入片上存储器。

该技术可用于基于MOS的工艺,因为氧化物必须很薄。最大的缺点是片上DAC很大——通常大于其调整的放大器电路。因此,EEPROM调整通常用于数据转换器或系统级产品,这种情况下DAC占总芯片面积的比例小得多。

图8总结了每种ADI调整方法的主要特点。可以看出,所有的调整方法都有各自适用的场合,目的是构建高性能线性集成电路。

| PROCESS        | TRIMMED AT:         | SPECIAL PROCESSING         | RESOLUTION |

|----------------|---------------------|----------------------------|------------|

| DigiTrim™      | Wafer or Final Test | None                       | Discrete   |

| Laser Trim     | Wafer               | Thin Film Resistor         | Continuous |

| Zener Zap Trim | Wafer               | None                       | Discrete   |

| Link Trim      | Wafer               | Thin Film or Poly Resistor | Discrete   |

| EEPROM Trim    | Wafer or Final Test | EEPROM                     | Discrete   |

图8: ADI调整工艺技术总结

## 参考文献:

- 1. Hank Zumbahlen, *Basic Linear Design*, Analog Devices, 2006, ISBN: 0-915550-28-1. Also available as *Linear Circuit Design Handbook*, Elsevier-Newnes, 2008, ISBN-10: 0750687037, ISBN-13: 978-0750687034. Chapter 1.

- 2. Walter G. Jung, *Op Amp Applications*, Analog Devices, 2002, ISBN 0-916550-26-5, Also available as *Op Amp Applications Handbook*, Elsevier/Newnes, 2005, ISBN 0-7506-7844-5. Chapter 1.

Copyright 2009, Analog Devices, Inc. All rights reserved. Analog Devices assumes no responsibility for customer product design or the use or application of customers' products or for any infringements of patents or rights of others which may result from Analog Devices assistance. All trademarks and logos are property of their respective holders. Information furnished by Analog Devices applications and development tools engineers is believed to be accurate and reliable, however no responsibility is assumed by Analog Devices regarding technical accuracy and topicality of the content provided in Analog Devices Tutorials.